Anton J.M. Montagne

2

basic design theory

design of application-specific amplifiers

in CMOS, Bipolar, and BiCMOS technology

in PCA technology

using SLiCAP (python) and SPICE

summary of background knowledge

TU DELFT

NSTITUTE

TU Delft OPEN

# Structured Electronics Design

A conceptual approach to amplifier design

# Structured Electronics Design

A conceptual approach to amplifier design

- basic design theory

- design of application-specific amplifiers

- in CMOS , Bipolar and BiCMOS technology

- in PCA technology

- using SLiCAP (python) and Spice

- summary of background knowledge

Anton J.M. Montagne

© Delft Academic Press / VSSD 1st edition 2018 2nd edition 2021

© TUDelft Open 2023 3rd edition ISBN 978-94-6366-712-8 (Ebook) ISBN 978-94-6366-711-1 (Paperback) DOI: https://doi.org/10.59490/t.2023.005

This work is licensed under a https://creativecommons.org/licenses/by/4.0/

Keywords: electronics, design

Scientific theories deal with concepts, never with reality. All theoretical results are derived from certain axioms by deductive logic. In physical sciences the theories are so formulated as to correspond in some useful sense to the real world, whatever that may mean. However, this correspondence is approximate, and the physical justification of all theoretical conclusions is based on some form of inductive reasoning.

A. Papoulis [Papoulis1965]<sup>1</sup>

<sup>1</sup> Athanasios Papoulis. *Probability Random Variables and Stochastic Processes*. McGraw-Hill, New York, 1965

To Ernst Nordholt

## Contents

| 1   | Introduction 1 |                                                                 |          |

|-----|----------------|-----------------------------------------------------------------|----------|

| 1.1 | Electronics    |                                                                 | 2        |

|     | 1.1.1          | Analog Electronics                                              | 2        |

|     | 1.1.2          | Structured design                                               | 3        |

|     | 1.1.3          | This chapter                                                    | 3        |

| 1.2 | Selecte        | d topics from systems engineering                               | 3        |

|     | 1.2.1          | Basic concepts                                                  | 4        |

|     | 1.2.2          | Basic design process                                            | 7        |

|     | 1.2.3          | Design data and documents                                       | 10       |

| 1.3 | Electro        | nic information processing                                      | 10       |

|     | 1.3.1          | Basic concepts                                                  | 11       |

|     | 1.3.2          | Limitations of information processing                           | 12       |

| 1.4 | Structu        | red Electronics Design                                          | 13       |

|     | 1.4.1          | Outline of the design language                                  | 13       |

|     | 1.4.2          | Basic functions and basic objects                               | 14       |

|     | 1.4.3          | Performance, costs, and FOM                                     | 16       |

|     | 1.4.4          | Error-reduction techniques                                      | 16       |

|     | 1.4.5<br>TI: 1 | Differences with traditional analog design                      | 17       |

| 1.5 | This bo        |                                                                 | 18       |

|     | 1.5.1          | What you will know after studying this book                     | 18       |

|     | 1.5.2          | Part 1: design of application-specific amplifiers               | 21<br>28 |

|     | 1.5.3<br>1.5.4 | Part 2: background knowledge<br>How to use this book            |          |

|     | 1.5.4          | How to use this book                                            | 29       |

|     | I De           | sign of application-specific amplifiers                         | 31       |

| 2   | Model          | ing and specification of amplifiers                             | 33       |

| 2.1 | Introdu        | action to amplifier design                                      | 35       |

|     | 2.1.1          | Functionality                                                   | 35       |

|     | 2.1.2          | Definition                                                      | 35       |

|     | 2.1.3          | Information-processing quality                                  | 36       |

|     | 2.1.4          | Physical appearance                                             | 36       |

|     | 2.1.5          | Cost factors and environmental conditions                       | 37       |

|     | 2.1.6          | Figure of merit                                                 | 37       |

|     | 2.1.7          | This chapter                                                    | 37       |

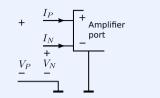

| 2.2 | -              | ier port requirements                                           | 38       |

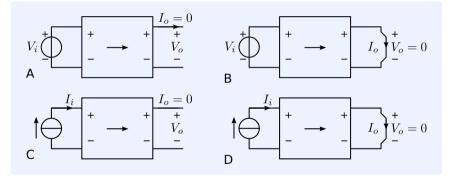

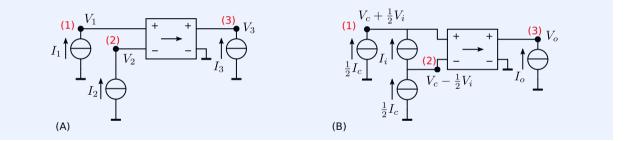

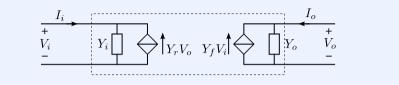

|     | 2.2.1          | Amplifier types                                                 | 40       |

|     | 2.2.2          | Ground<br>Port configurations                                   | 41       |

|     | 2.2.3<br>2.2.4 | Summing and distributing signals                                | 41       |

| 2.2 | •              | ng of the ideal behavior                                        | 43       |

| 2.3 |                | 0                                                               | 44       |

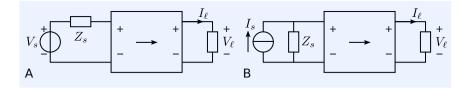

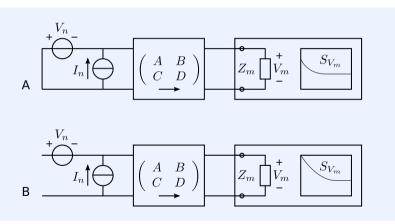

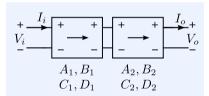

|     | 2.3.1          | Transmission matrix-1 representation<br>Source-to-load transfer | 44       |

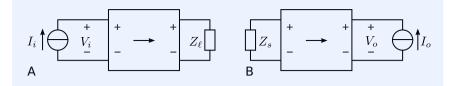

|     | 2.3.2<br>2.3.3 | Input and output impedance                                      | 45<br>46 |

|     | 2.3.3          | Available power gain                                            | 48<br>48 |

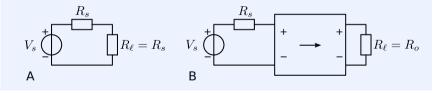

|     | 2.3.5          | Idealized amplifier models                                      | 40<br>50 |

|     | ~ ~ ~          | 1                                                               | 9        |

| 2.4         | Modeling   | ; of the non-ideal behavior                        | 52         |

|-------------|------------|----------------------------------------------------|------------|

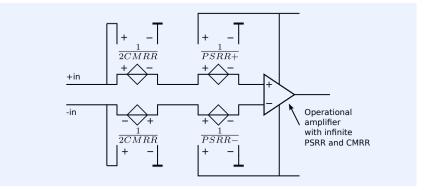

|             | 2.4.1 I    | Modeling of the source and load isolation          | 53         |

|             | 2.4.2 I    | Modeling of the power supply isolation             | 54         |

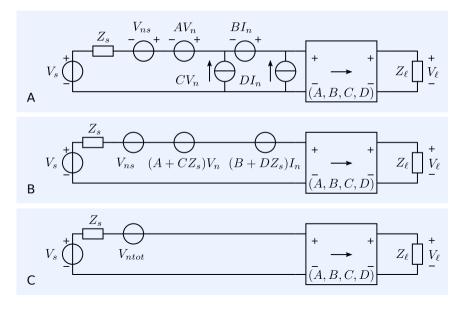

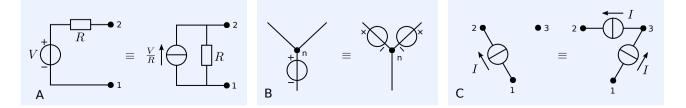

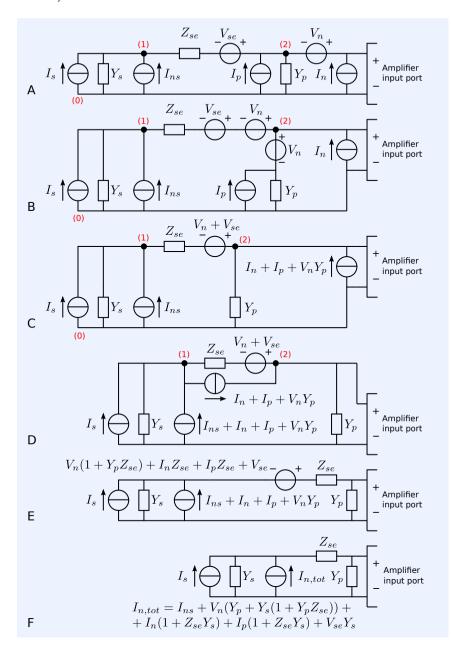

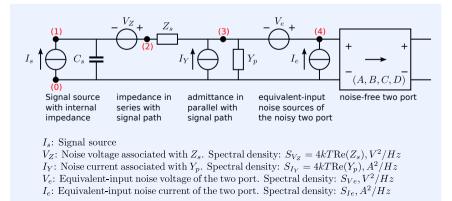

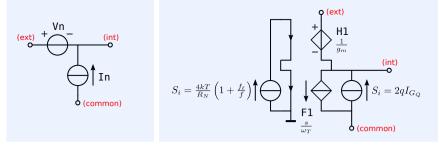

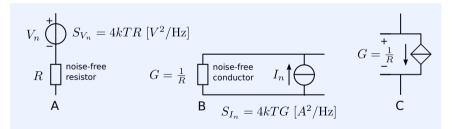

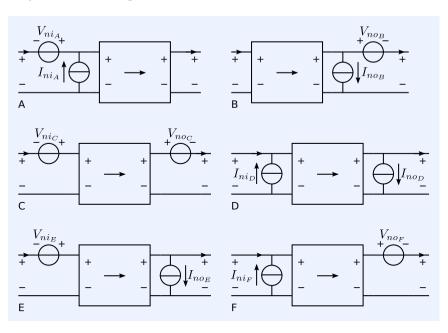

|             | 2.4.3 I    | Modeling of the noise behavior                     | 56         |

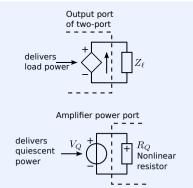

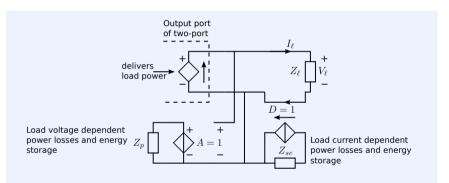

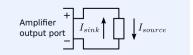

|             |            | Modeling of the power efficiency                   | 65         |

|             |            | Power losses and amplifier classes                 | 67         |

|             |            | Modeling of the small-signal dynamic behavior      | 69         |

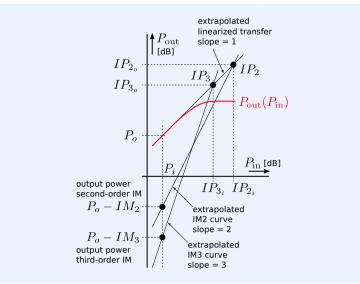

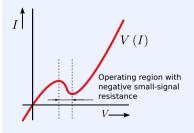

|             |            | Modeling of the static nonlinear behavior          | 71         |

|             |            | Modeling of the dynamic nonlinear dynamic behavior | 75         |

|             |            | Modeling of temperature effects                    | 77         |

|             |            | Ageing                                             | 77         |

| 2.5         | Cascaded   | Amplifiers                                         | 77         |

|             | 2.5.1 I    | Port isolation                                     | 78         |

|             | 9          | Noise behavior                                     | 79         |

|             |            | Small-signal dynamic behavior                      | 80         |

|             | 51         | Static nonlinear behavior                          | 80         |

| 2.6         | Amplifier  | requirement specification                          | 80         |

|             | 2.6.1 (    | Operational requirements                           | 80         |

|             | 2.6.2 I    | Requirements from other life cycle processes       | 83         |

| 3           | Amplific   | ation Mechanism                                    | 85         |

| 3.1         | Introduct  | ion                                                | 86         |

| 5           | 3.1.1      | Active devices                                     | 86         |

|             | 5          | This chapter                                       | 86         |

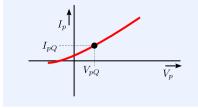

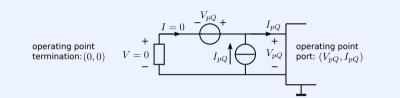

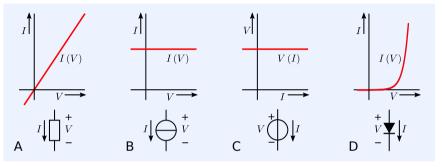

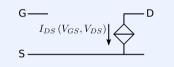

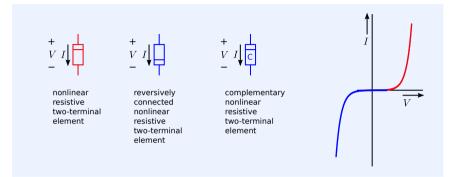

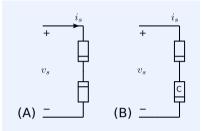

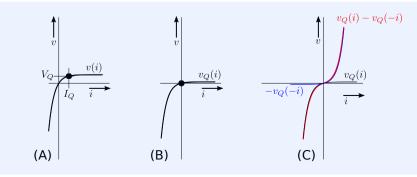

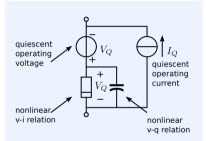

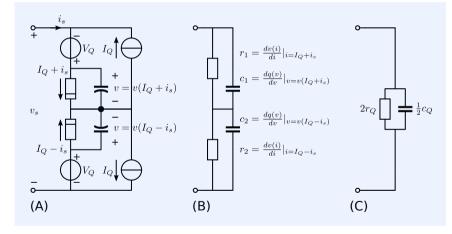

| 3.2         |            | inal resistive elements                            | 86         |

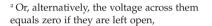

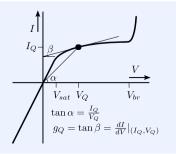

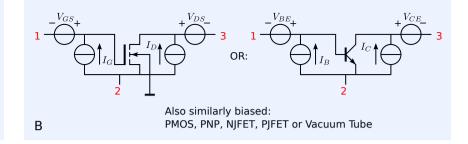

| <i>J</i> .= |            | Voltage-controlled and current-controlled notation | 87         |

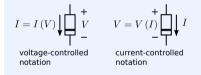

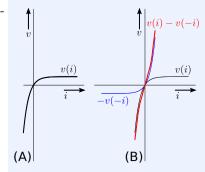

|             |            | Resistive two-terminal elements                    | 87         |

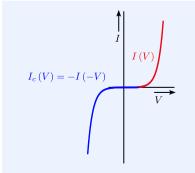

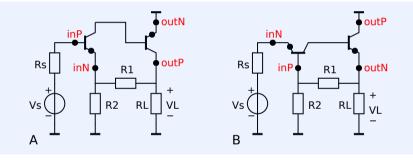

|             | 5          | Complementary devices                              | 88         |

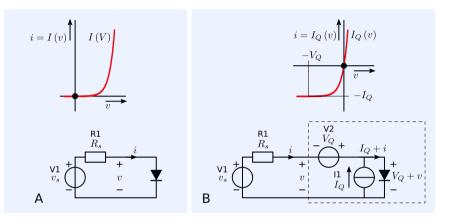

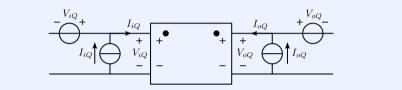

|             |            | Operating point                                    | 88         |

|             | ÷ .        | Linearization and available power gain             | 90         |

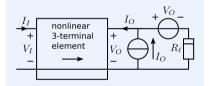

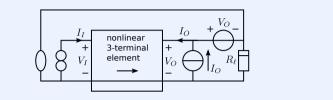

| 3.3         |            | minal resistive elements                           | 91         |

| 5.5         |            | Complementary multi-terminal elements              | 91         |

|             |            | Resistive two-ports                                | 91<br>91   |

|             |            | Complementary two-ports                            | 91         |

|             |            | Operating point                                    | 91         |

|             |            | Linearization and available power gain             | 92         |

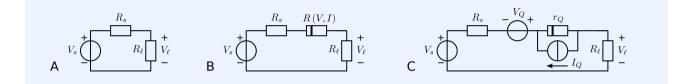

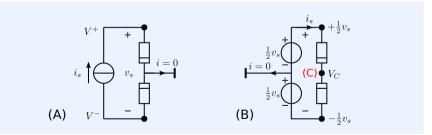

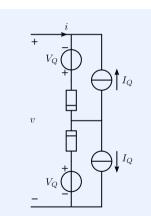

| 3.4         |            | ion to biasing                                     | 93         |

| 7.4         |            | Independent and dependent bias sources             | 93         |

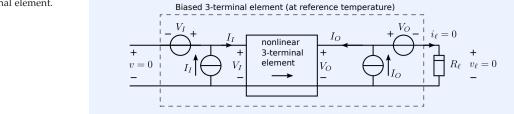

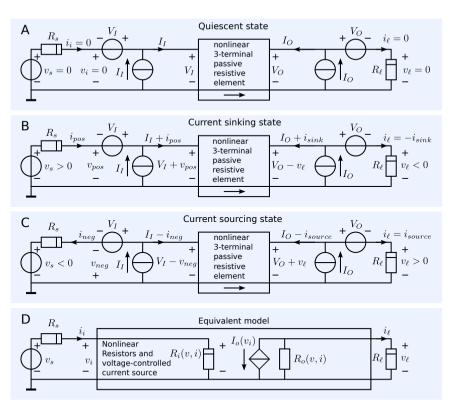

|             |            | Biasing of 3-terminal elements                     | 93<br>94   |

|             | ÷ .        | Amplification mechanism                            | 94         |

|             |            | Deriving the bias sources from the power supply    | 95         |

| 3.5         | Conclusio  | · · · · · ·                                        | 96         |

| J.J         |            | Generalized biased active device                   | 96<br>96   |

| 4           | Active D   | Devices                                            | 97         |

|             | Introduct  |                                                    | 98         |

| 4.1         |            | Design equations and symbolic circuit analysis     | 90<br>98   |

|             |            | Numeric circuit analysis                           | -          |

|             |            | Simulation accuracy                                | 99<br>99   |

|             |            | This chapter                                       | 99<br>100  |

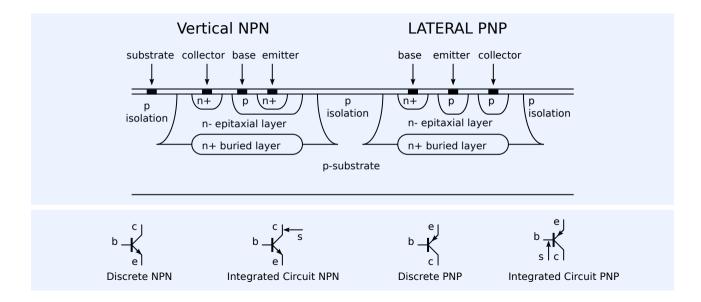

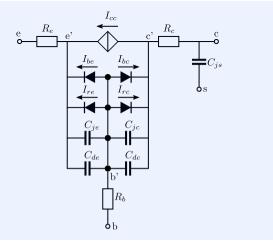

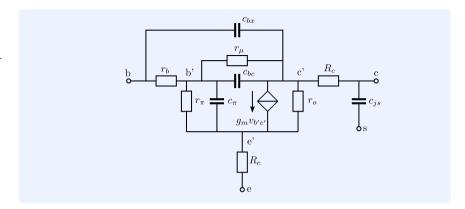

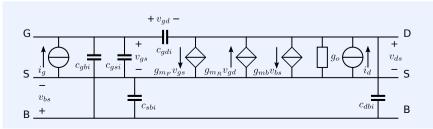

| 1 2         | Bipolar tr | -                                                  | 100        |

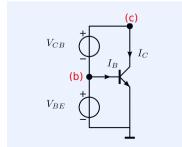

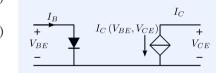

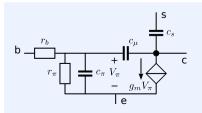

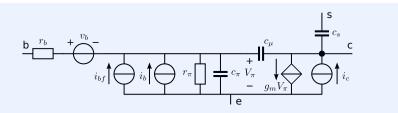

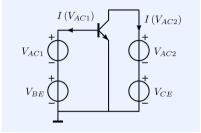

| 4.2         | -          |                                                    |            |

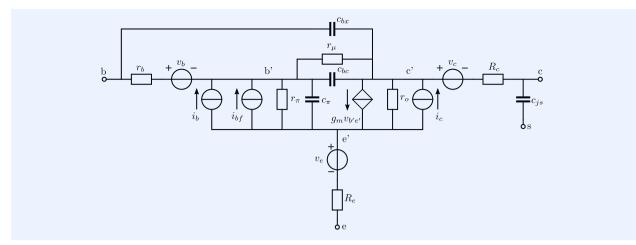

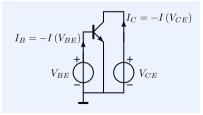

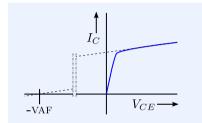

|             |            | Operation<br>Gummel-Poon model                     | 100<br>101 |

|             |            | Device parameters                                  | 101        |

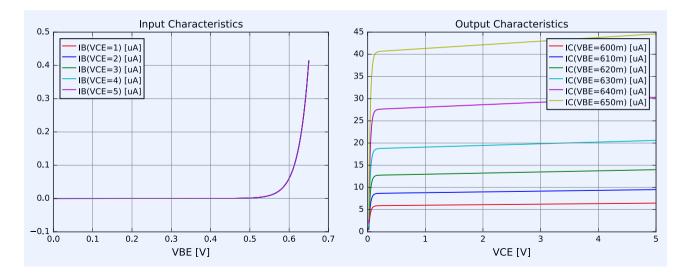

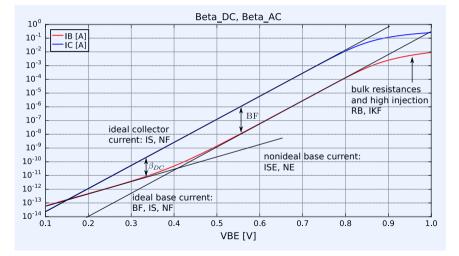

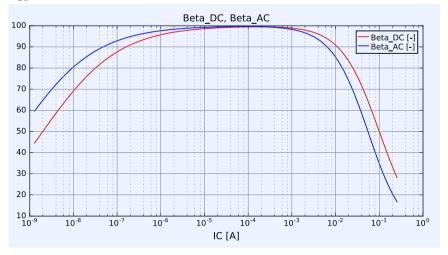

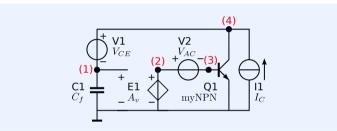

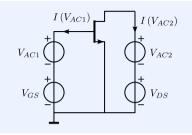

|             |            | Simulated device characteristics                   | 100        |

|             |            | Other models                                       | 112        |

|             |            | Simplified models for hand calculations            | 112        |

|             | -          | -                                                  |            |

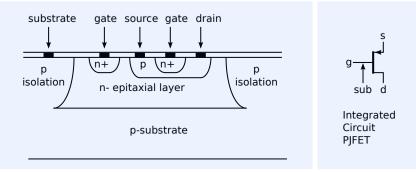

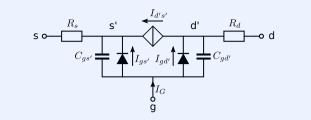

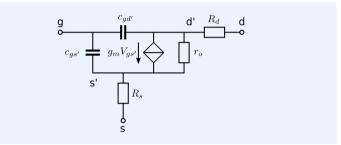

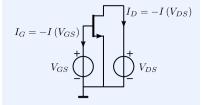

| 4.3 | Junctio          | n Field Effect Transistors                                          | 115        |

|-----|------------------|---------------------------------------------------------------------|------------|

|     | 4.3.1            | IFET simulation model                                               | 115        |

|     | 4.3.2            | Device parameters                                                   | 119        |

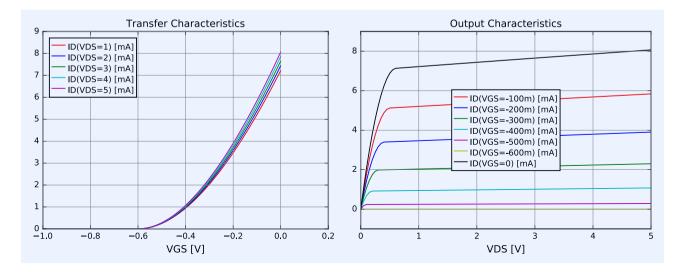

|     | 4.3.3            | JFET simulated device characteristics                               | 119        |

|     | 4.3.4            | Simplified models for hand calculation                              | 121        |

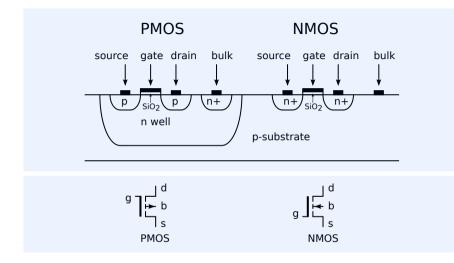

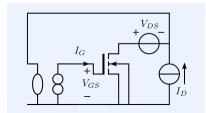

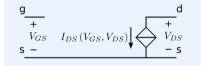

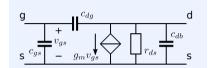

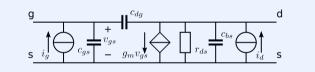

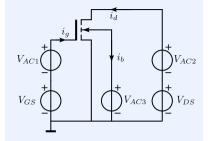

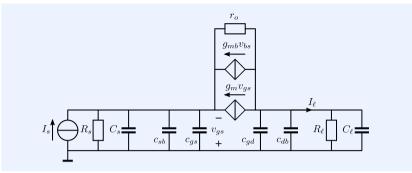

| 4.4 | MOS ta           | ransistors                                                          | 123        |

|     | 4.4.1            | Operation                                                           | 124        |

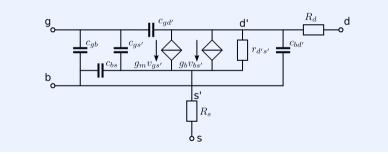

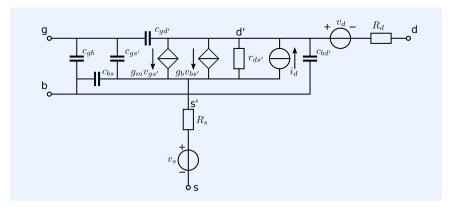

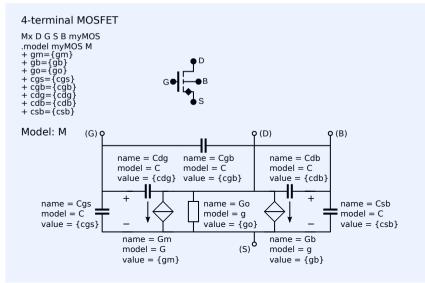

|     | 4.4.2            | MOSFET modeling                                                     | 125        |

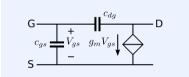

|     | 4.4.3            | MOSFET level 1 model                                                | 126        |

|     | 4.4.4            | Device parameters                                                   | 130        |

|     | 4.4.5            | Simplified models for hand calculations                             | 132        |

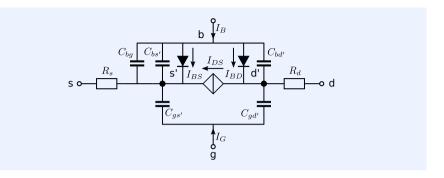

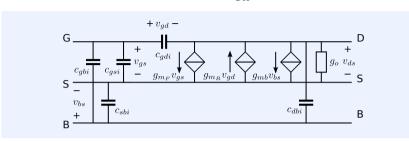

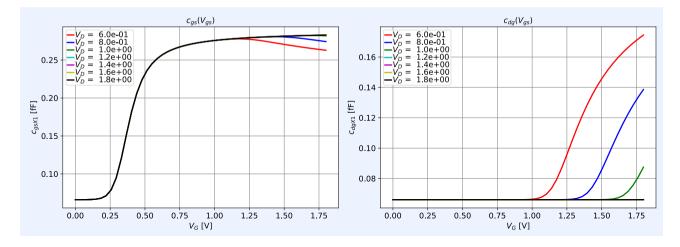

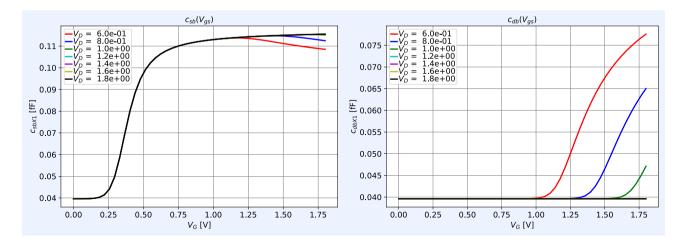

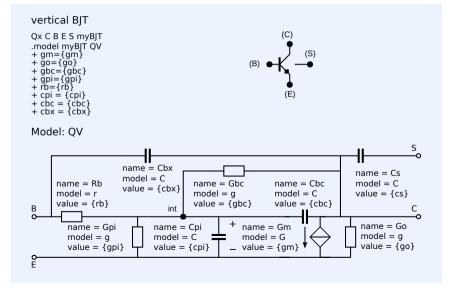

|     | 4.4.6            | Capacitance models                                                  | 135        |

|     | 4.4.7            | MOS EKV Model                                                       | 137        |

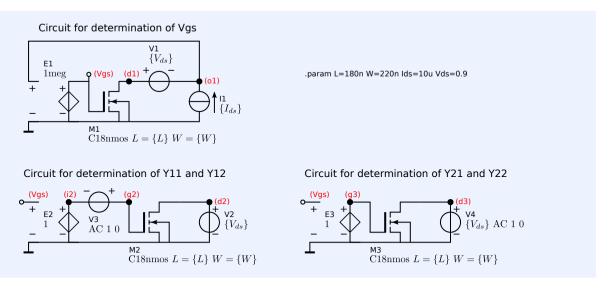

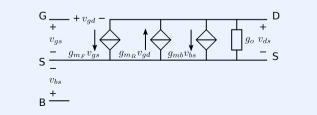

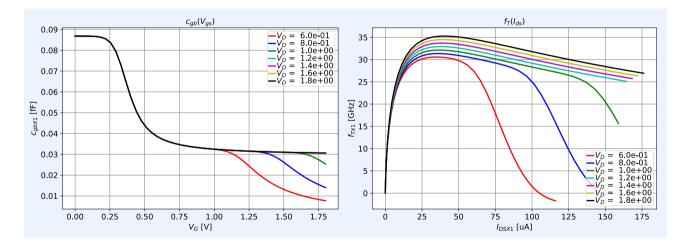

| 4.5 | SLiCA.           | P device models                                                     | 146        |

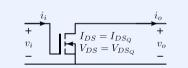

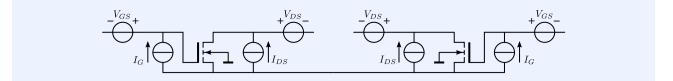

|     | 4.5.1            | Signal path and biasing                                             | 147        |

|     | 4.5.2            | SLiCAP parametric small-signal models                               | 147        |

|     | 4.5.3            | BJT forward region, no saturation                                   | 147        |

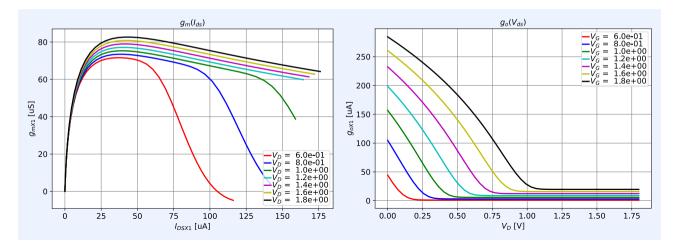

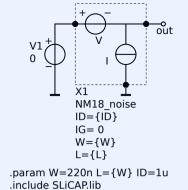

|     | 4.5.4            | NMOS EKV forward region, saturation range                           | 148        |

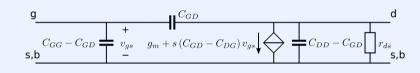

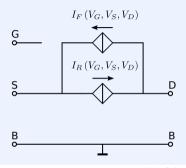

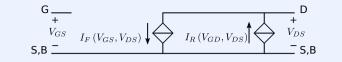

|     | 4.5.5            | NMOS EKV forward region, linear and saturation range                | 151        |

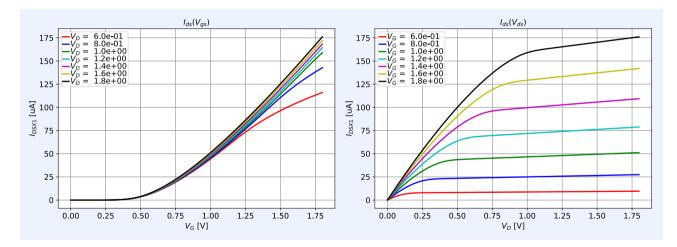

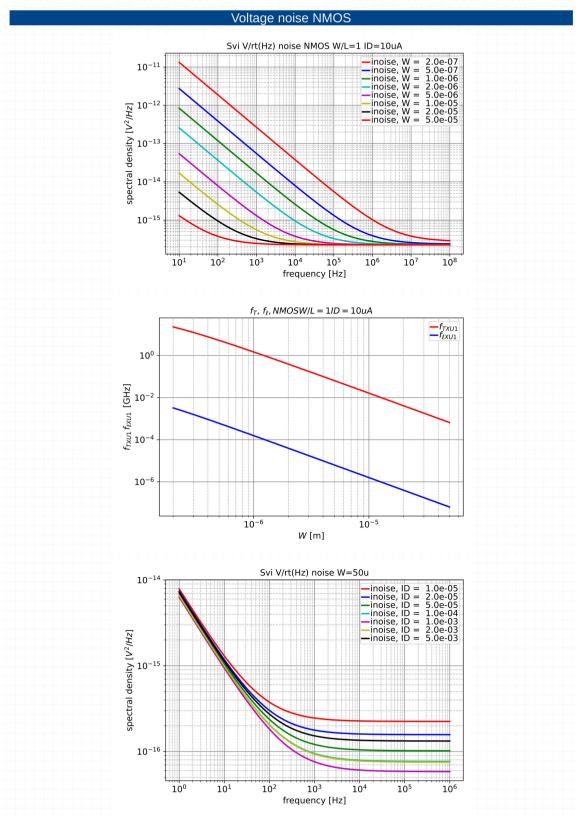

|     | 4.5.6            | SLICAP MOS device characteristics                                   | 153        |

|     | 4.5.7            | PMOS EKV models                                                     | 154        |

| 4.6 | Conclu           | isions                                                              | 155        |

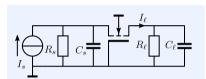

| 5   | Basic a          | amplification: CS stage                                             | 159        |

| -   | Introdu          |                                                                     |            |

| 5.1 |                  |                                                                     | 160        |

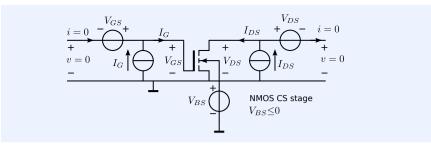

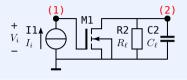

|     | 5.1.1            | The CS stage                                                        | 160<br>160 |

|     | 5.1.2<br>The int | This chapter                                                        |            |

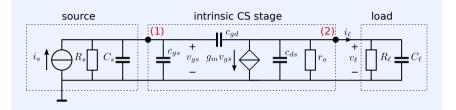

| 5.2 |                  | trinsic CS stage                                                    | 160        |

|     | 5.2.1            | Instantaneous behavior                                              | 163        |

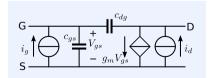

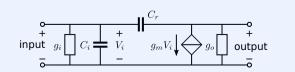

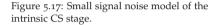

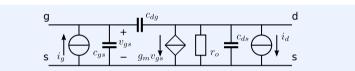

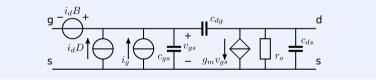

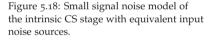

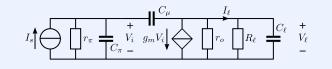

|     | 5.2.2            | Small-signal dynamic behavior                                       | 166        |

|     | 5.2.3            | Large-signal dynamic behavior<br>Noise behavior                     | 170        |

|     | 5.2.4<br>Care 11 |                                                                     | 172        |

| 5.3 |                  | signal behavior of CS stage between source and load                 | 176        |

|     | 5.3.1            | Transimpedance                                                      | 177        |

|     | 5.3.2            | Current gain                                                        | 177        |

|     | 5.3.3            | Qualitative description of the dynamic behavior                     | 178        |

|     | 5.3.4            | Quantitative description of the dynamic behavior<br>Input impedance | 178<br>182 |

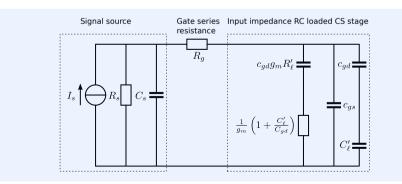

|     | 5.3.5<br>5.3.6   | Influence of the gate series resistance                             | 184        |

|     |                  | -                                                                   |            |

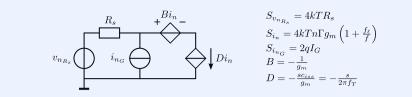

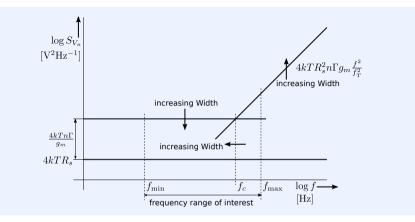

| 5.4 | -                | ization of the noise performance of a CS stage                      | 184        |

|     | 5.4.1            | Noise design considerations                                         | 185        |

|     | 5.4.2            | Noise minimization for resistive source                             | 185        |

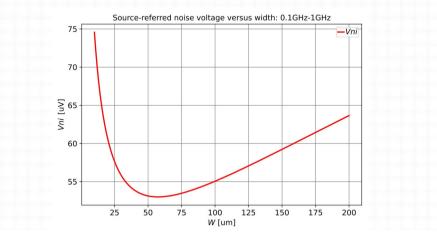

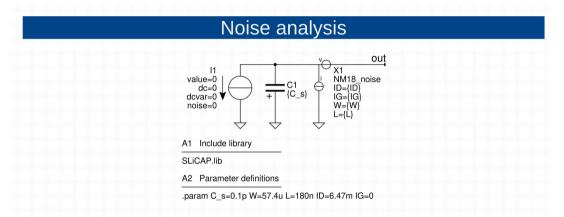

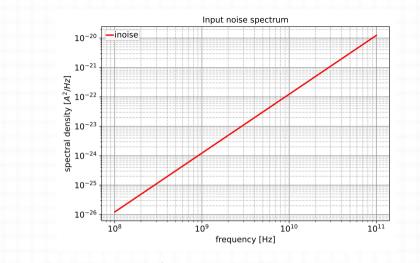

|     | 5.4.3            | Noise minimization for capacitive voltage source                    | 195        |

|     | 5.4.4<br>Conclu  | Noise minimization for capacitive current source                    | 200        |

| 5.5 | Conciu           | ISIONS                                                              | 204        |

| 6   | Balanc           | ing techniques                                                      | 205        |

| 6.1 | Introdu          | action                                                              | 206        |

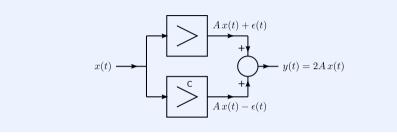

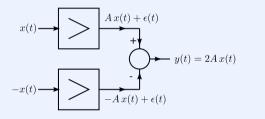

|     | 6.1.1            | Additive compensation                                               | 206        |

|     | 6.1.2            | Balancing                                                           | 206        |

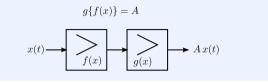

|     | 6.1.3            | Multiplicative or cascaded compensation                             | 207        |

|     | 6.1.4            | Odd function synthesis                                              | 207        |

|     | 6.1.5            | This chapter                                                        | 208        |

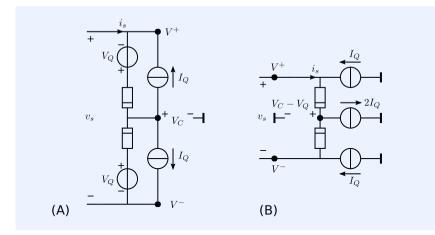

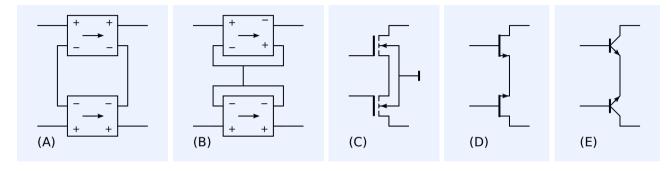

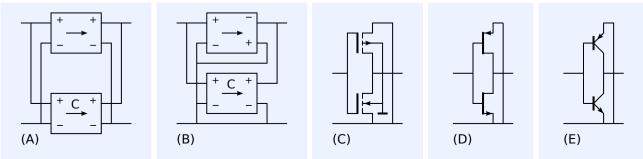

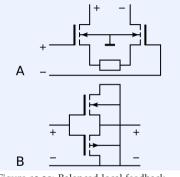

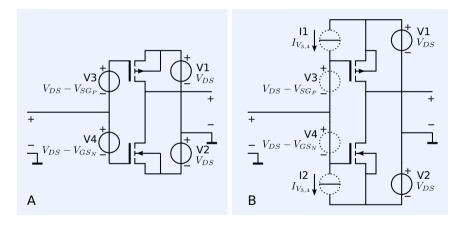

| 6.2 | Balanc           | ing of two-terminal devices                                         | 208        |

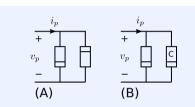

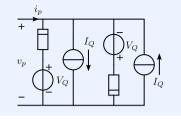

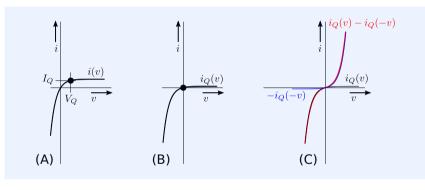

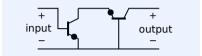

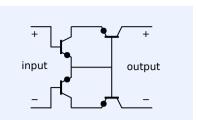

|     | 6.2.1            | Anti-series and complementary-series connection                     | 209        |

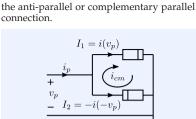

|     | 6.2.2            | Anti-parallel and complementary-parallel connection                 | 213        |

| 6.3      | Balanc         | ing of two-ports                                            | 216        |

|----------|----------------|-------------------------------------------------------------|------------|

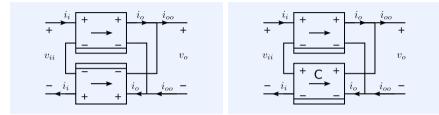

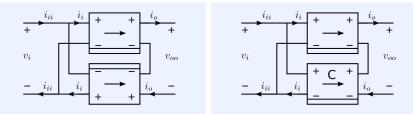

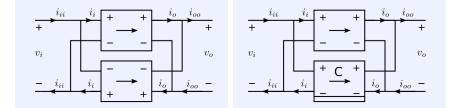

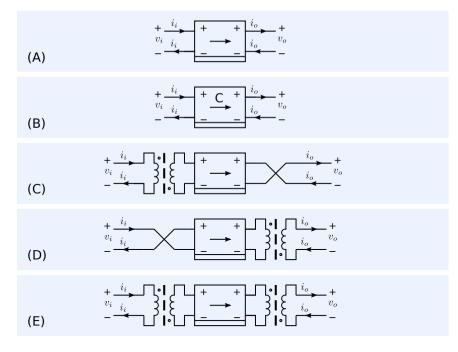

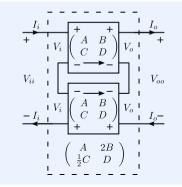

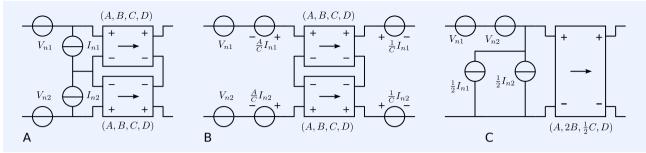

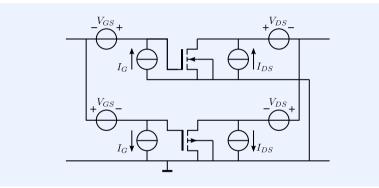

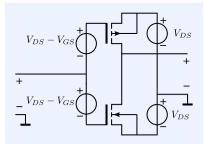

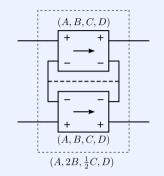

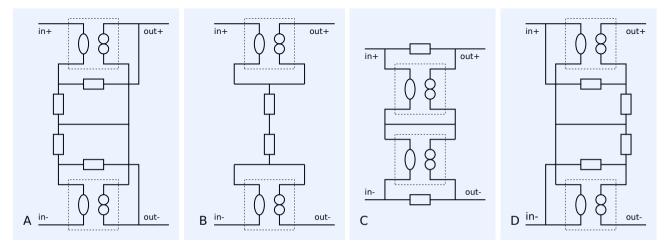

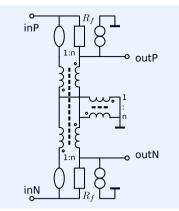

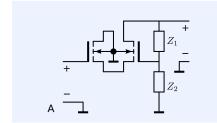

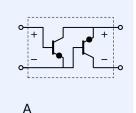

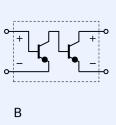

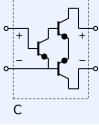

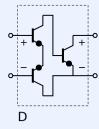

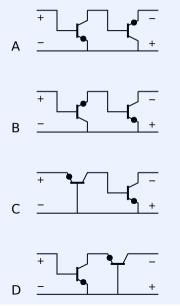

|          | 6.3.1          | Balanced two-port configurations                            | 216        |

|          | 6.3.2          | Design of complementary two-ports                           | 217        |

| 6.4      | Balanc         | ed CE and CS stages                                         | 218        |

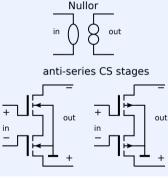

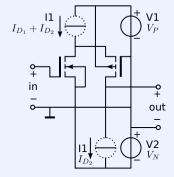

|          | 6.4.1          | Anti-series stages                                          | 218        |

|          | 6.4.2          | Anti-series CS stage                                        | 220        |

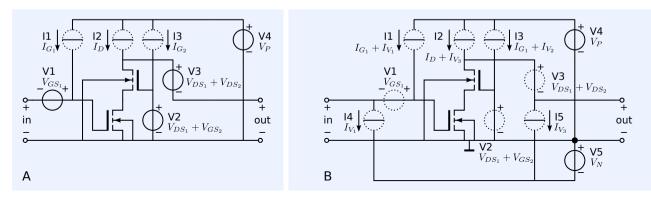

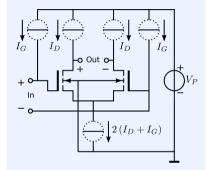

|          | 6.4.3          | Complementary-parallel stages                               | 223        |

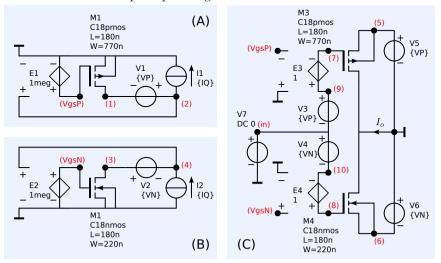

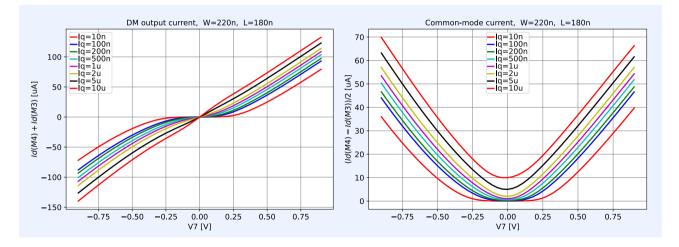

|          | 6.4.4          | Complementary-parallel CS stage                             | 224        |

| 6.5      | Conclu         | isions                                                      | 228        |

| 7        | Desig          | n of feedback amplifier configurations                      | 229        |

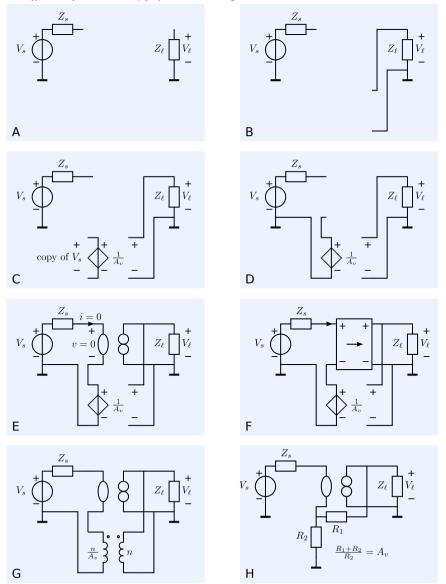

| 7.1      | Introd         | uction                                                      | 231        |

|          | 7.1.1          | Design tasks                                                | 231        |

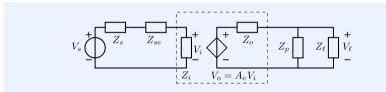

|          | 7.1.2          | Brute force port impedance design                           | 231        |

|          | 7.1.3          | Negative feedback amplifiers                                | 233        |

|          | 7.1.4          | This chapter                                                | 233        |

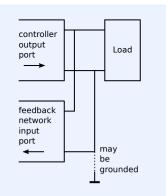

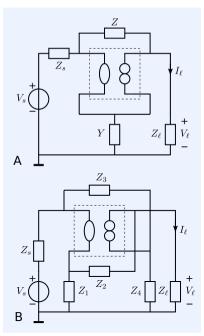

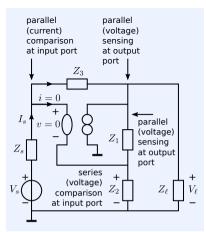

| 7.2      | Desigr         | of feedback configurations                                  | 234        |

|          | 7.2.1          | Step-by-step design of the feedback configuration           | 234        |

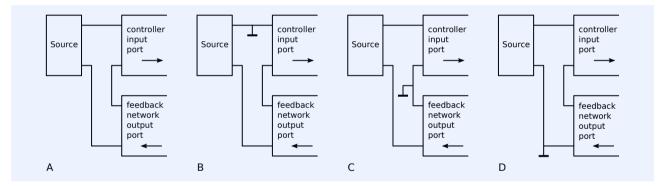

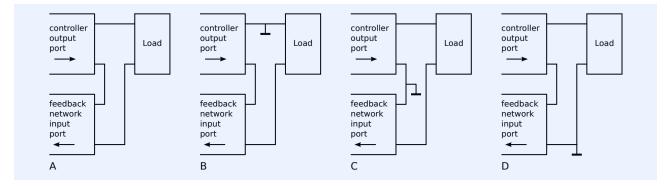

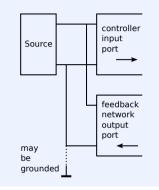

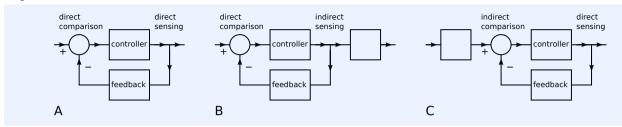

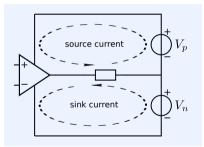

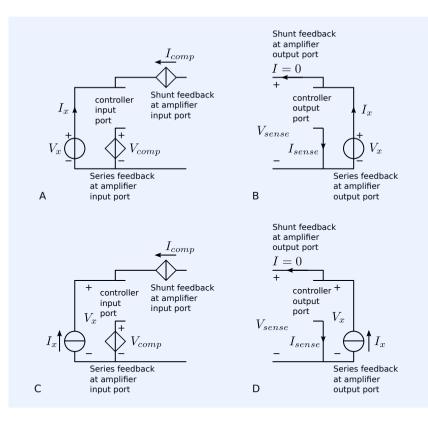

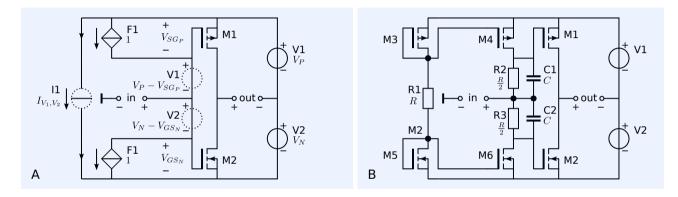

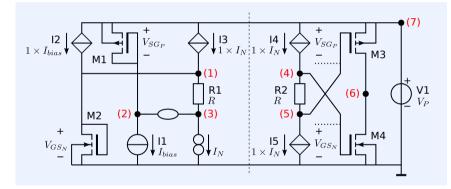

|          | 7.2.2          | Direct sensing and comparison techniques                    | 237        |

|          | 7.2.3          | Indirect sensing and comparison techniques                  | 239        |

| 7.3      | Impler         | nentation of negative feedback                              | 239        |

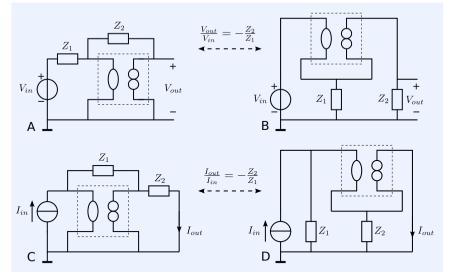

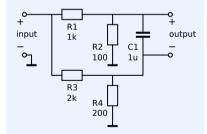

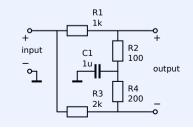

|          | 7.3.1          | Feedback networks                                           | 240        |

|          | 7.3.2          | Ideal gain of a feedback amplifier                          | 240        |

|          | 7.3.3          | Negative and positive feedback                              | 241        |

| 7.4      | Nonen          | ergic feedback                                              | 241        |

|          | 7.4.1          | Design of nonenergic amplifier configurations               | 242        |

|          | 7.4.2          | Noise behavior of nonenergic feedback amplifiers            | 243        |

|          | 7.4.3          | Power efficiency of nonenergic feedback amplifiers          | 243        |

| 7.5      | Passive        | e feedback                                                  | 243        |

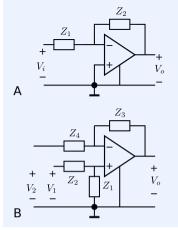

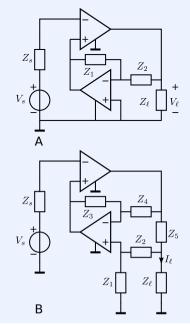

|          | 7.5.1          | Single-loop passive feedback configurations                 | 244        |

|          | 7.5.2          | Noise behavior of passive feedback configurations           | 245        |

|          | 7.5.3          | Power efficiency of passive feedback configurations         | 255        |

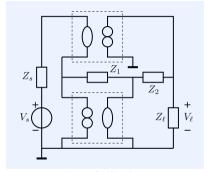

|          | 7.5.4          | Dual-loop passive feedback configurations                   | 256        |

| 7.6      | Active         | feedback                                                    | 257        |

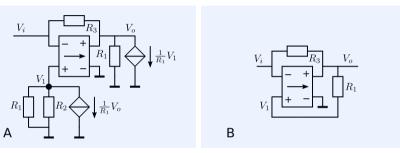

|          | 7.6.1          | Single-loop active feedback                                 | 257        |

|          | 7.6.2          | Multiple-loop active feedback                               | 258        |

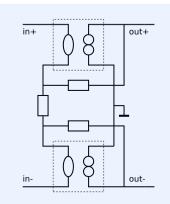

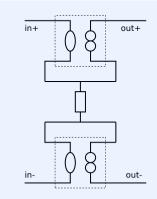

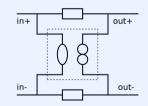

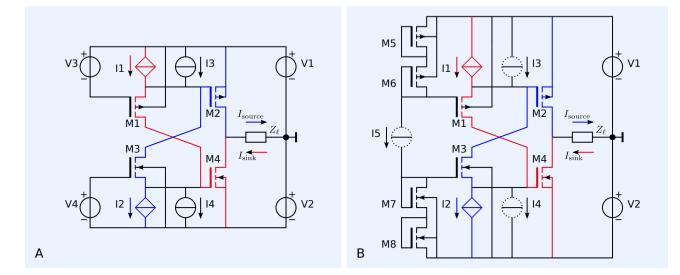

| 7.7      | -              | n of balanced amplifiers                                    | 259        |

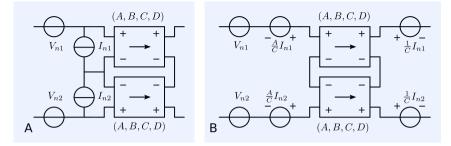

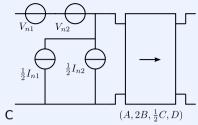

|          | 7.7.1          | Anti-series connected amplifiers                            | 259        |

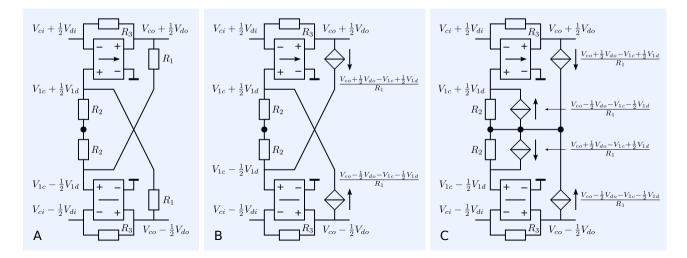

|          | 7.7.2          | Balanced single-loop configurations                         | 260        |

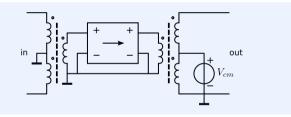

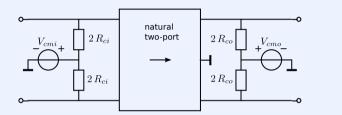

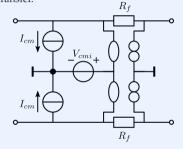

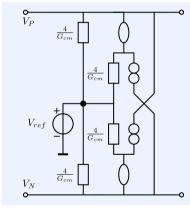

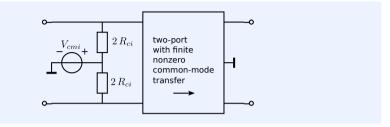

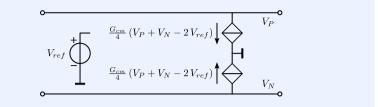

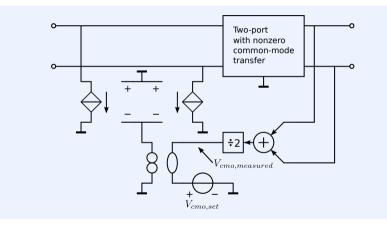

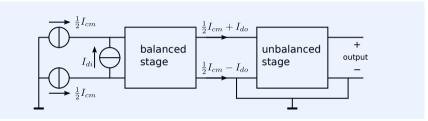

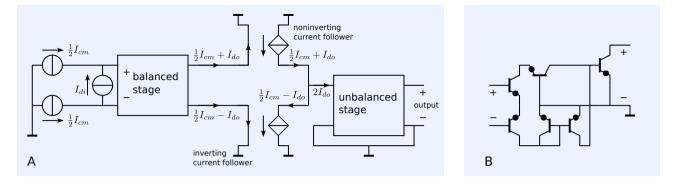

|          | 7.7.3          | Common-mode behavior of balanced amplifiers                 | 261        |

|          | 7.7.4          | Design of natural two-ports                                 | 266        |

|          | 7.7.5          | Dual-loop balanced passive feedback amplifiers              | 267        |

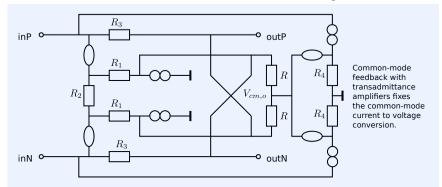

| _ 0      | 7.7.6          | Design of common-mode port impedances                       | 269        |

| 7.8      |                | t feedback                                                  | 269        |

|          | 7.8.1<br>7.8.2 | Indirect sensing<br>Indirect comparison                     | 270<br>270 |

| 0        |                | *                                                           |            |

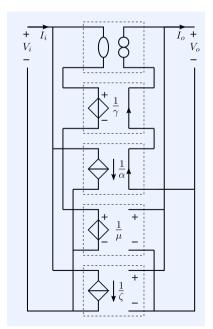

| 8<br>8.1 | Introd         | cation and specification of operational amplifiers          | 271        |

| 0.1      |                |                                                             | 272        |

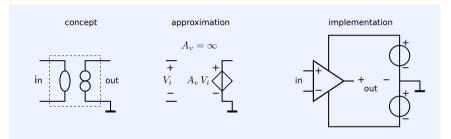

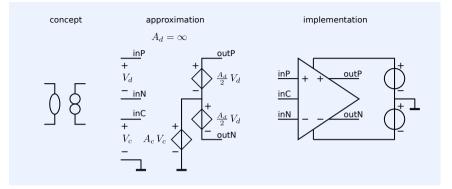

|          | 8.1.1          | Operational Amplifier types                                 | 272        |

|          | 8.1.2<br>8.1.3 | Idealized models<br>This chapter                            | 273        |

| 8 ~      | -              | *                                                           | 274        |

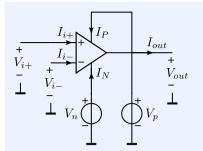

| 8.2      |                | cterization of operational amplifiers                       | 274        |

|          | 8.2.1          | Commonly used terms                                         | 275        |

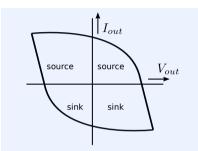

|          | 8.2.2<br>8.2.3 | Terminal voltages and currents<br>Static nonlinear behavior | 275<br>276 |

|          | 0.2.3          | Swate nonlinear benavior                                    | 2/0        |

|          | 8.2.4            | Noise and small-signal dynamic behavior                     | 276        |

|----------|------------------|-------------------------------------------------------------|------------|

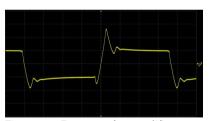

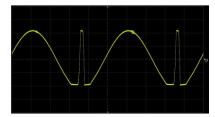

|          | 8.2.5            | Large-signal dynamic behavior                               | 277        |

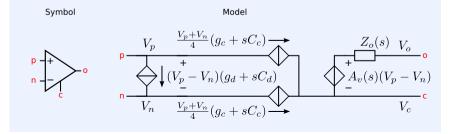

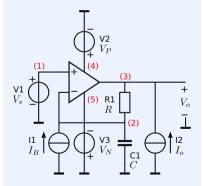

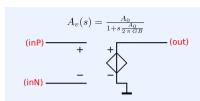

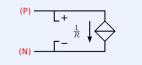

| 8.3      | Modeli           | ng of the operational amplifier                             | 277        |

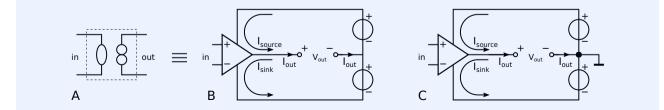

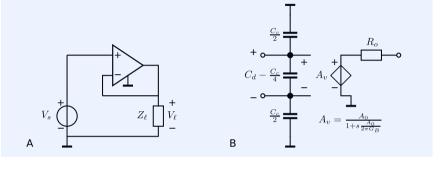

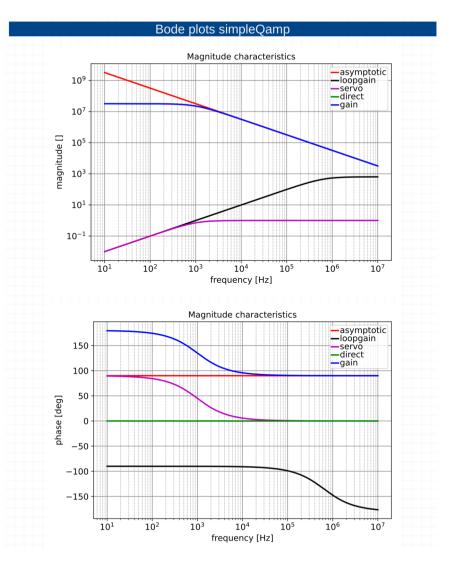

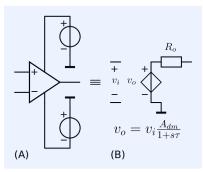

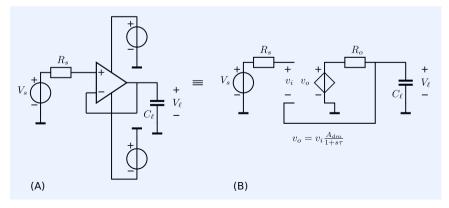

|          | 8.3.1            | Small-signal dynamic behavior                               | 278        |

|          | 8.3.2            | Noise behavior                                              | 282        |

|          | 8.3.3            | PSRR and CMRR                                               | 284        |

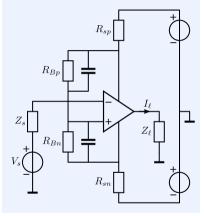

|          | 8.3.4            | Bias and offset quantities                                  | 284        |

|          | 8.3.5<br>8.3.6   | Modeling of other effects<br>Macro models                   | 285<br>285 |

| 0.       |                  |                                                             | 285        |

| 8.4      | -                | of feedback configurations with Op-Amps                     | 286        |

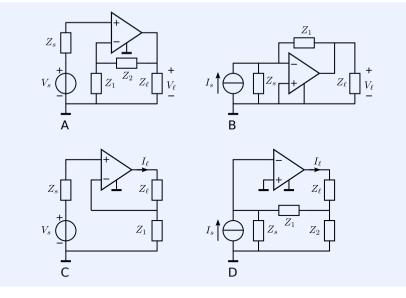

|          | 8.4.1            | Single-loop passive feedback configurations                 | 286        |

|          | 8.4.2            | Active feedback amplifier configurations                    | 288        |

| 9        | Introdu          | uction to amplifier biasing                                 | 291        |

| 9.1      | Introdu          | lection                                                     | 292        |

|          | 9.1.1            | This chapter                                                | 293        |

| 9.2      | Basic te         | chniques                                                    | 293        |

| -        | 9.2.1            | Basic biasing technique                                     | 293        |

|          | 9.2.2            | DC coupling and AC coupling                                 | 294        |

|          | 9.2.3            | Deriving bias quantities from the power supply              | 295        |

| 9.3      | Evaluat          | tion of biasing errors                                      | 298        |

| / 0      | 9.3.1            | Power supply and resistor tolerances                        | 299        |

|          | 9.3.2            | Controller bias imperfections                               | 305        |

|          | 9.3.3            | Total biasing error                                         | 307        |

|          | 9.3.4            | Biasing design limits and budgets                           | 308        |

| 9.4      | Applica          | ation of error reduction techniques                         | 309        |

| <i>.</i> | 9.4.1            | Negative feedback and auto-zero biasing                     | 310        |

|          | 9.4.2            | Modulation and demodulation techniques                      | 312        |

| 9.5      | Commo            | on-mode biasing                                             | 313        |

|          | 9.5.1            | AC coupling                                                 | 313        |

|          | 9.5.2            | DC-coupled floating port amplifiers                         | 313        |

| 10       | Model            | ing of negative feedback circuits                           | 317        |

| 10.1     | Introdu          |                                                             | 318        |

|          | 10.1.1           | Two-step design approach                                    | 318        |

|          | 10.1.2           | This chapter                                                | 319        |

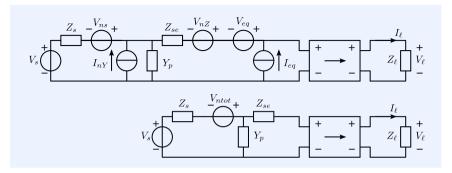

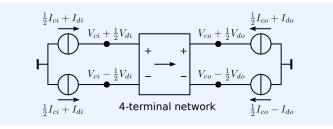

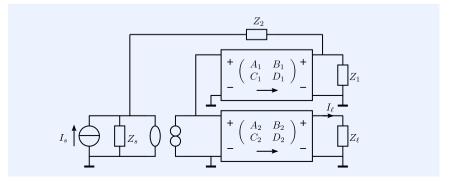

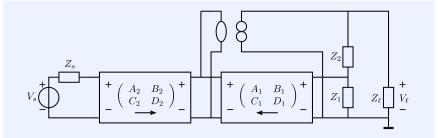

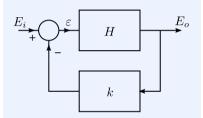

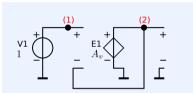

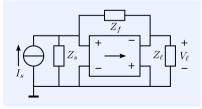

| 10.2     |                  | feedback model                                              | 319        |

| 10.2     | 10.2.1           | Model description                                           |            |

|          | 10.2.1           | Application of the model                                    | 319<br>320 |

|          | 10.2.3           | Conclusions                                                 | 323        |

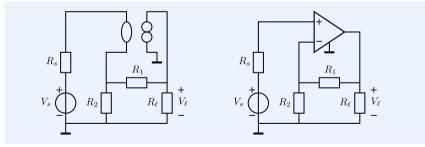

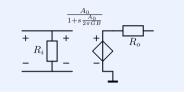

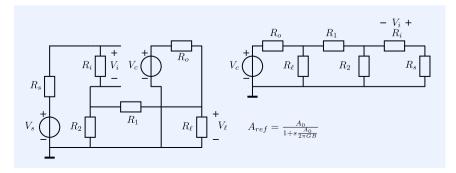

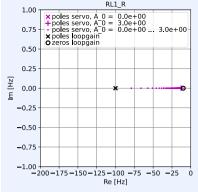

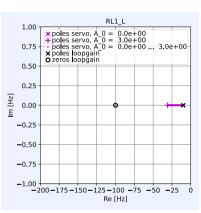

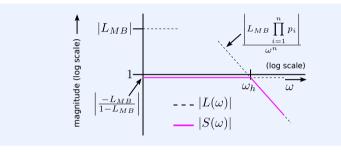

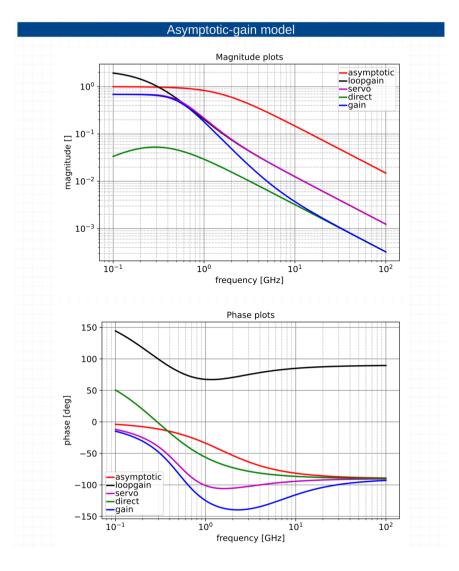

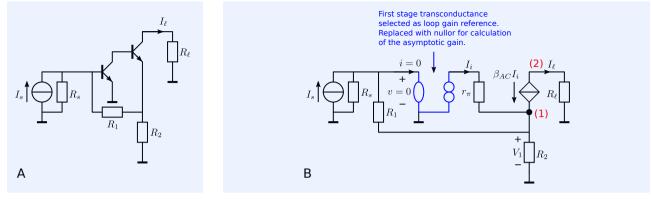

| 10.3     | -                | totic gain model                                            | 324        |

| 10.5     |                  | Superposition model                                         | •••        |

|          | 10.3.1<br>10.3.2 | Asymptotic gain model                                       | 324<br>326 |

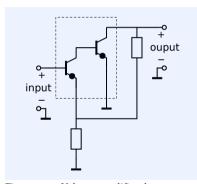

|          | 10.3.3           | Selection of the loop gain reference                        | 327        |

|          | 10.3.4           | Hand calculations of the loop gain                          | 334        |

|          | 10.3.5           | Impedance model                                             | 338        |

|          | 10.3.6           | Port impedance of single-loop feedback amplifiers           | 341        |

|          | 10.3.7           | Port impedance of multi-loop feedback amplifiers            | 343        |

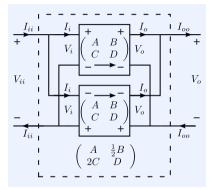

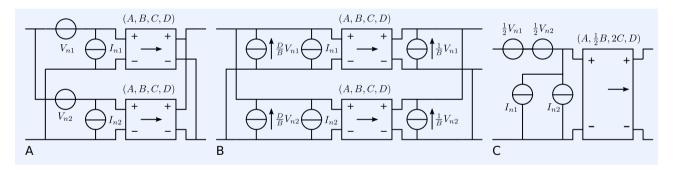

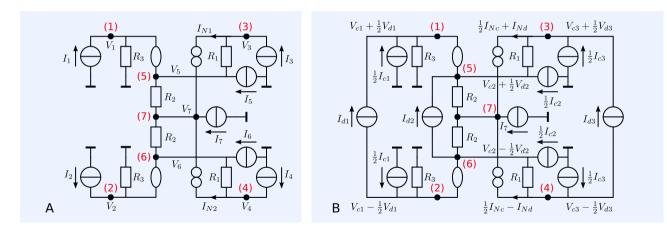

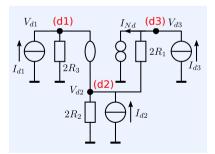

|          | 10.3.8           | Application of asymptotic gain model in balanced amplifiers | 344        |

|          | 10.3.9           | Asymptotic gain model and network analysis                  | 345        |

|          | 10.3.10          | Conclusions                                                 | 348        |

| 11       | Ampli            | fier performance and controller requirements                | 349        |

| 11.1     | Introdu          | iction                                                      | 350        |

|          | 11.1.1           | This chapter                                                | 350        |

| 11.2 | Accura           | cy design considerations                                                           | 351        |

|------|------------------|------------------------------------------------------------------------------------|------------|

|      | 11.2.1           | Static inaccuracy of the servo function                                            | 351        |

|      | 11.2.2           | Design conclusion                                                                  | 352        |

| 11.3 | Nonlin           | earity design consideration                                                        | 352        |

|      | 11.3.1           | Loop gain differential gain error                                                  | 352        |

|      | 11.3.2           | Design conclusion                                                                  | 353        |

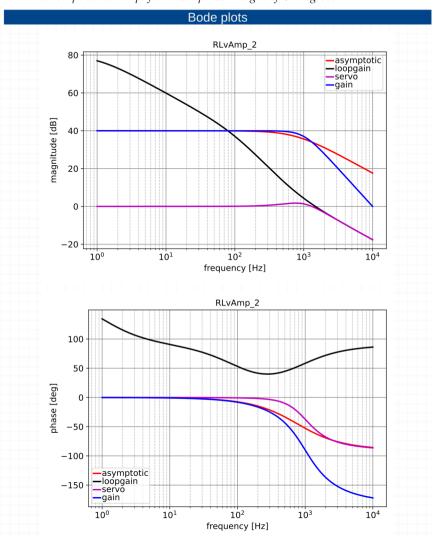

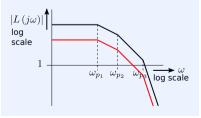

| 11.4 | Bandw            | idth design considerations                                                         | 353        |

|      | 11.4.1           | Midband frequency range and bandwidth                                              | 354        |

|      | 11.4.2           | All-pole loop gain functions                                                       | 354        |

|      | 11.4.3           | Low-pass cut-off and loop gain-poles product<br>High-pass cut-off and DC loop gain | 355        |

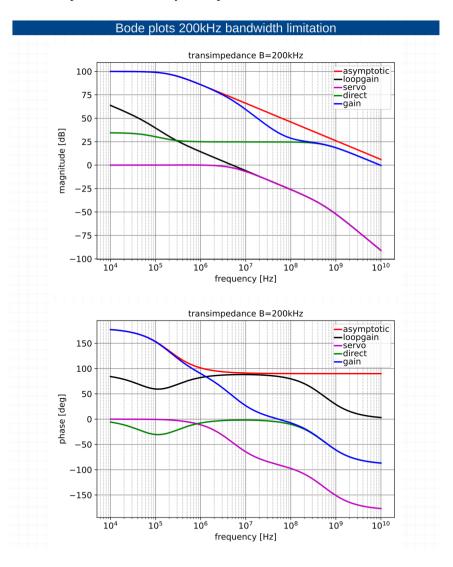

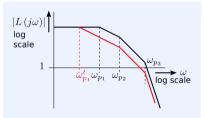

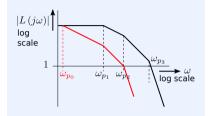

|      | 11.4.4<br>11.4.5 | Low-pass cut-off with poles and zeros                                              | 364<br>369 |

|      | 11.4.6           | High-pass cut-off with poles and zeros                                             | 370        |

|      | 11.4.7           | Procedure for determination of the servo bandwidth                                 | 370        |

|      | 11.4.8           | Design conclusions                                                                 | 372        |

| 11.5 | Stabilit         | y of negative feedback amplifiers                                                  | 372        |

|      | 11.5.1           | Routh–Hurwitz criterion                                                            | 373        |

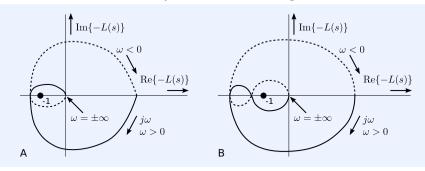

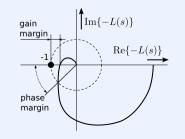

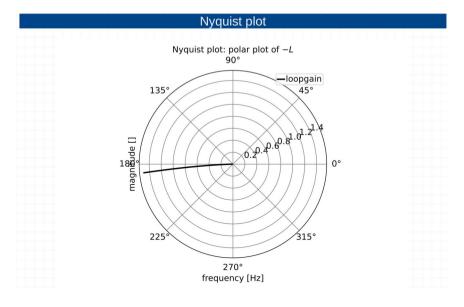

|      | 11.5.2           | Nyquist criterion                                                                  | 374        |

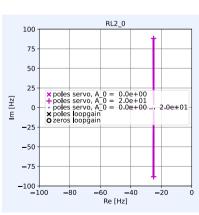

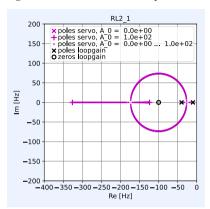

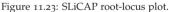

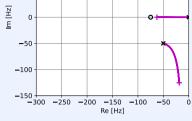

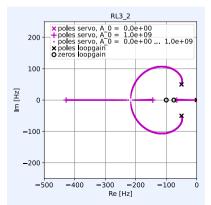

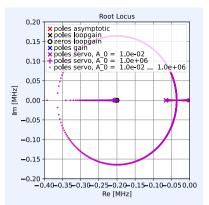

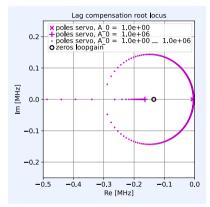

|      | 11.5.3           | Root locus analysis                                                                | 376        |

|      | 11.5.4           | Non-observable and non-controllable states                                         | 380        |

|      | 11.5.5           | Design conclusions                                                                 | 381        |

| 12   | Freque           | ency compensation                                                                  | 383        |

| 12.1 | Introdu          |                                                                                    | 385        |

|      | 12.1.1           | Filter design approach                                                             | 386        |

|      | 12.1.2           | Compensation techniques                                                            | 388        |

|      | 12.1.3           | Compensation strategies                                                            | 389        |

|      | 12.1.4           | This chapter                                                                       | 389        |

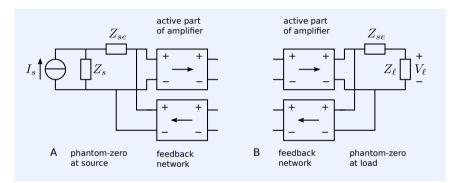

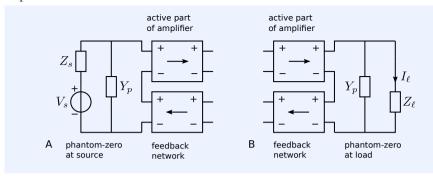

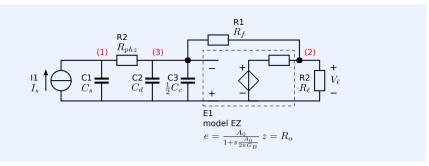

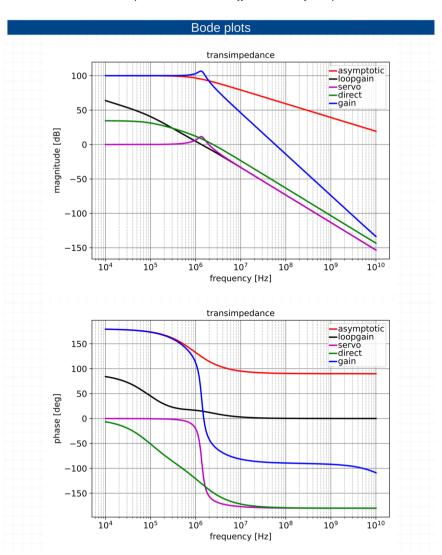

| 12.2 | Phanto           | m zero compensation                                                                | 390        |

|      | 12.2.1           | The phantom zero concept                                                           | 390        |

|      | 12.2.2           | Second order compensation                                                          | 391        |

|      | 12.2.3           | Third order compensation                                                           | 397        |

|      | 12.2.4<br>12.2.5 | Implementation of phantom zeros<br>Phantom zeros in the feedback network           | 405<br>406 |

|      | 12.2.9           | Phantom zeros at source and load                                                   | 400        |

|      | 12.2.7           | Active phantom zeros                                                               | 420        |

|      | 12.2.8           | Interaction with other performance aspects                                         | 421        |

|      | 12.2.9           | Bandwidth limitation with phantom zeros                                            | 422        |

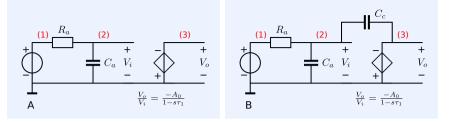

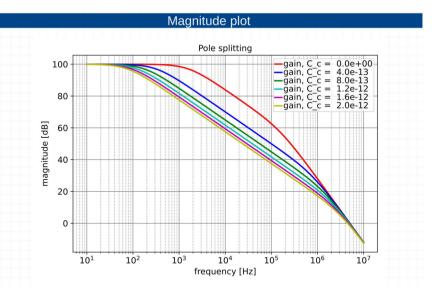

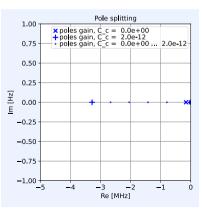

| 12.3 | Pole-sp          | olitting                                                                           | 424        |

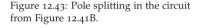

|      | 12.3.1           | Pole-splitting in operational amplifier circuits                                   | 425        |

|      | 12.3.2           | Miller effect                                                                      | 426        |

|      | 12.3.3           | Interaction with other performance aspects                                         | 427        |

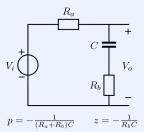

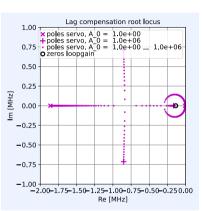

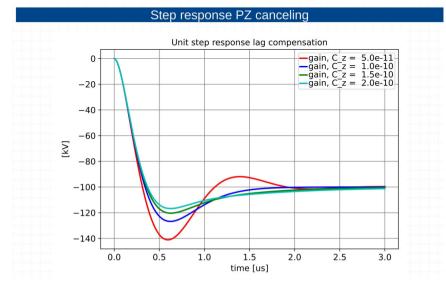

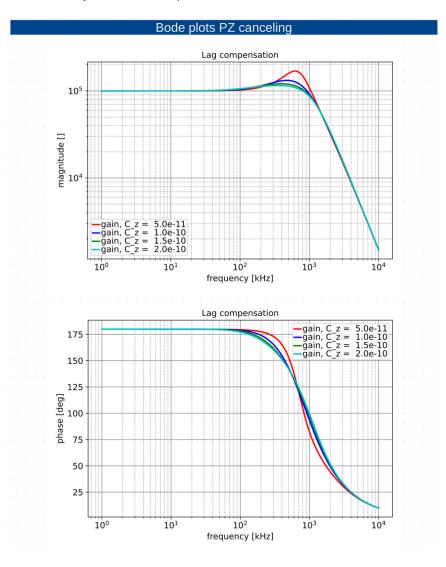

| 12.4 | Pole-ze          | ero canceling                                                                      | 427        |

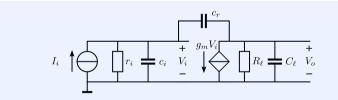

|      | 12.4.1           | Insertion of impedances into the signal path                                       | 428        |

|      | 12.4.2           | Interaction with other performance aspects                                         | 431        |

| 12.5 |                  | ve broadbanding                                                                    | 432        |

|      | 12.5.1           | Insertion of resistors into the signal path                                        | 432        |

|      | 12.5.2<br>Dlasa  | Interaction with other performance aspects                                         | 432        |

| 12.6 |                  | margin design                                                                      | 432        |

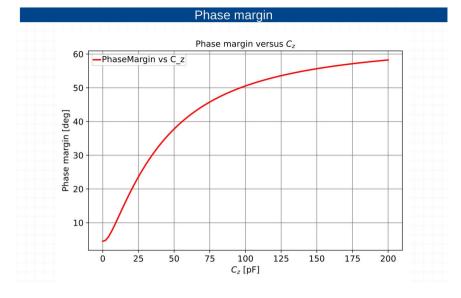

|      | 12.6.1           | Lag and lead compensators                                                          | 433        |

|      | 12.6.2<br>Deduct | Interaction with other performance aspects                                         | 437        |

| 12.7 |                  | ion of the servo bandwidth                                                         | 437        |

|      | 12.7.1           | Excessive pole-splitting<br>Pole frequency reduction                               | 437        |

|      | 12.7.2<br>12.7.3 | Pole frequency reduction<br>DC loop gain reduction                                 | 437<br>438 |

|      | 12.7.4           | Interaction with other performance aspects                                         | 438        |

|      |                  | · ·                                                                                |            |

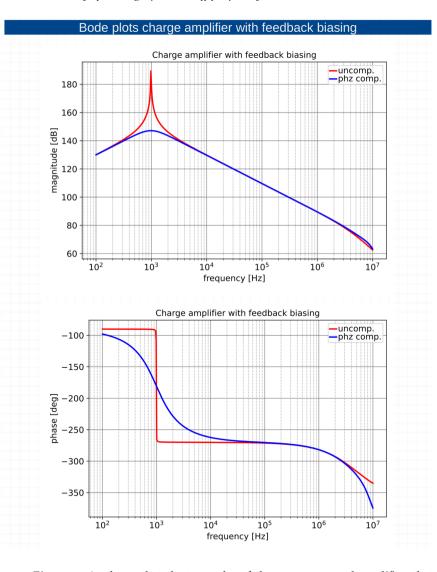

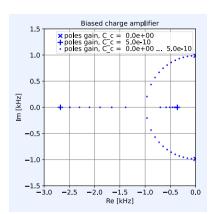

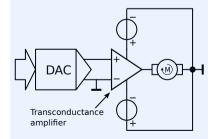

| 12.8  | Feedbac          | k biasing frequency compensation                                                 | 438        |

|-------|------------------|----------------------------------------------------------------------------------|------------|

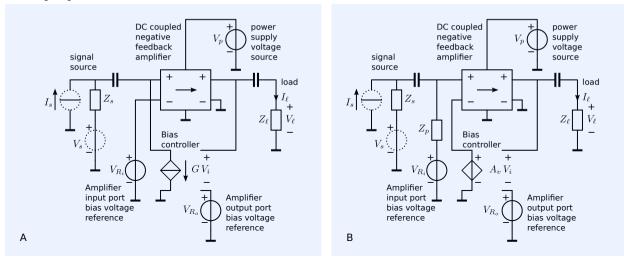

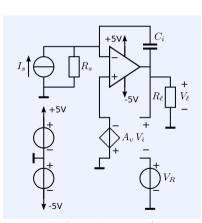

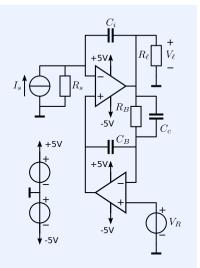

|       | 12.8.1           | Negative feedback biasing concepts                                               | 438        |

|       | 12.8.2           | Dynamic behavior with feedback biasing                                           | 439        |

| 12.9  | Nested of        |                                                                                  | 443        |

|       | 12.9.1           | 1                                                                                | 443        |

|       | 12.9.2           | Increasing bandwidth without adding dominant poles                               | 446        |

|       | 12.9.3<br>Common | Interaction with other performance aspects                                       | 446        |

| 12.10 | 12.10.1          | nsation for open and shorted ports<br>Compensation of shorted ports              | 447        |

|       | 12.10.1          | Compensation of open ports                                                       | 447<br>448 |

| 12.11 |                  | e of non dominant poles                                                          | 448        |

| 12.11 | 12.11.1          | Bandwidth limitation with phantom zeros                                          | 448        |

| 10    | Local fe         | eedback stages                                                                   | 140        |

| 13    |                  |                                                                                  | 449        |

| 13.1  | Introduc         |                                                                                  | 450        |

|       | 13.1.1<br>13.1.2 | Local feedback amplifier stages<br>This chapter                                  | 450        |

| 10.0  | 5                | eedback stages                                                                   | 450        |

| 13.2  |                  | Nonenergic feedback stages                                                       | 451        |

|       | 13.2.1<br>13.2.2 | Common Drain Stage                                                               | 451<br>452 |

|       | 13.2.3           | Common Gate Stage                                                                | 458        |

|       | 13.2.4           | Passive feedback stages                                                          | 461        |

| 13.3  | Applica          | tion of balancing                                                                | 462        |

|       | 13.3.1           | Local feedback with balanced CS stage                                            | 462        |

|       | 13.3.2           | Balanced local feedback amplifier stages                                         | 462        |

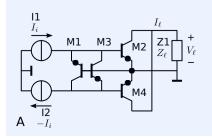

| 13.4  | Indirect         | feedback stages                                                                  | 463        |

|       | 13.4.1           | Current mirror                                                                   | 463        |

|       | 13.4.2           | Voltage mirror                                                                   | 463        |

| 14    | Multi-s          | tage Feedback Amplifiers                                                         | 465        |

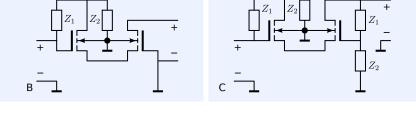

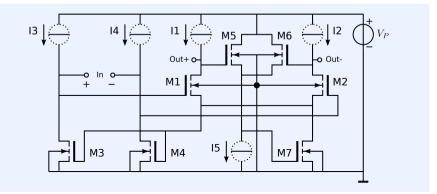

| 14.1  | Introduc         | ction                                                                            | 466        |

|       | 14.1.1           | Summary of previous chapters                                                     | 466        |

|       | 14.1.2           | This chapter                                                                     | 471        |

| 14.2  | Controll         | ler design considerations                                                        | 472        |

|       | 14.2.1           | Design of the input stage                                                        | 473        |

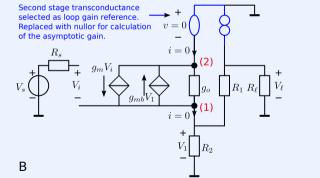

|       | 14.2.2           | Design of the output stage                                                       | 473        |

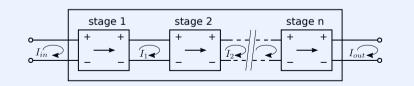

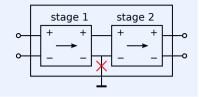

|       | 14.2.3           | Design of the number of stages                                                   | 474        |

|       | 14.2.4           | Interconnection of stages<br>Interconnection of controller and feedback networks | 476<br>480 |

|       | 14.2.5<br>14.2.6 | Cascode stages                                                                   | 480<br>481 |

|       | 14.2.7           | Application of local feedback stages                                             | 482        |

| 15    | Amplif           | ier Biasing                                                                      | 485        |

| 15.1  | Introduc         | 0                                                                                | 486        |

| 1).1  | 15.1.1           | A structured approach to biasing                                                 | 486        |

|       | 15.1.2           | Basic passive biasing elements                                                   | 486        |

|       | 15.1.3           | Outline of the biasing approach                                                  | 488        |

|       | 15.1.4           | Drawing conventions                                                              | 488        |

|       | 15.1.5           | This chapter                                                                     | 489        |

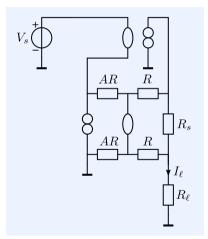

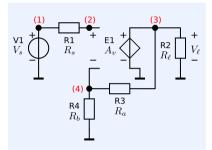

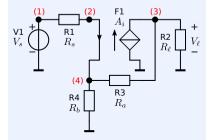

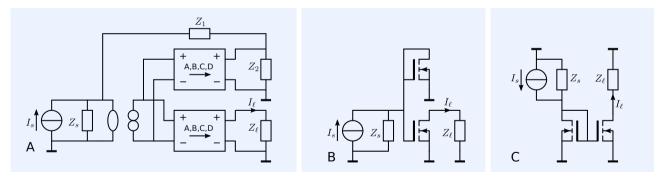

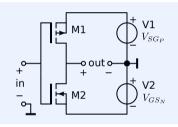

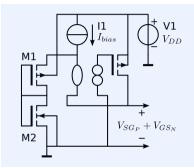

| 15.2  | Setting 1        | up the initial biasing scheme                                                    | 489        |

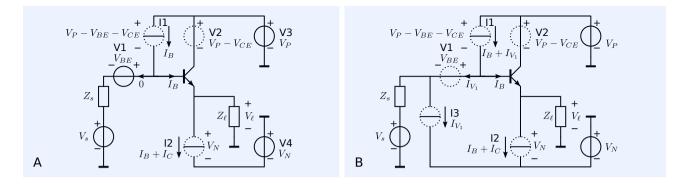

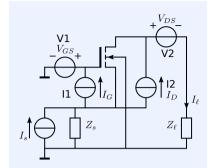

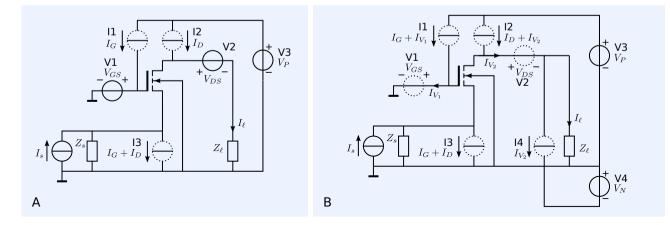

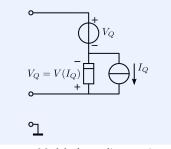

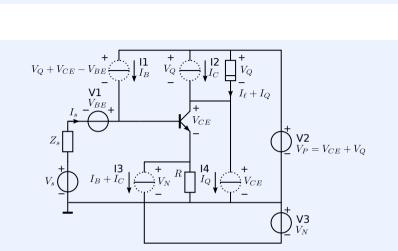

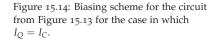

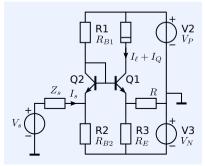

|       | 15.2.1           | CE and CS stage biasing                                                          | 490        |

|       | 15.2.2           | Biasing of local-feedback stages                                                 | 491        |

|       | 15.2.3           | Biasing of cascode stages                                                        | 495        |

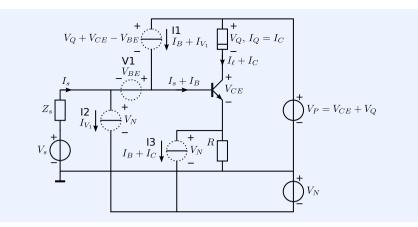

|       | 15.2.4<br>15.2.5 | Biasing of anti-series stages<br>Biasing of complementary-parallel stages        | 496<br>500 |

|       |                  | Smoning of completionary purater burgeo                                          |            |

|      | II Background knowledge                                 | 505          |  |  |

|------|---------------------------------------------------------|--------------|--|--|

| 16   | Signal Modeling (selected topics)                       |              |  |  |

| 16.1 | Introduction                                            |              |  |  |

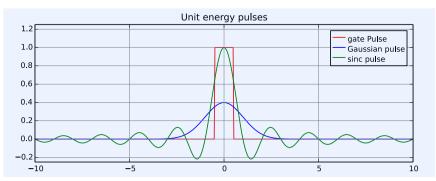

| 16.2 | Deterministic signal modeling                           | 508<br>508   |  |  |

| 10.2 | 16.2.1 Power signals and energy signals                 | 509          |  |  |

|      | 16.2.2 Time-domain modeling of signals                  | 510          |  |  |

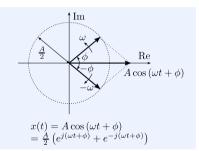

|      | 16.2.3 Frequency-domain modeling of signals             | 511          |  |  |

|      | 16.2.4 Cosine transformation                            | 512          |  |  |

|      | 16.2.5 Fourier transform                                | 512          |  |  |

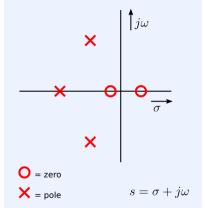

|      | 16.2.6 Complex frequency domain modeling                | 514          |  |  |

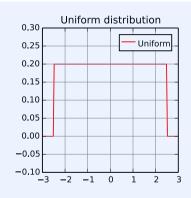

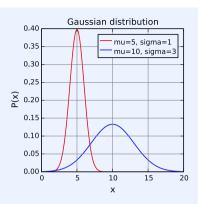

| 16.3 | Random signal modeling                                  | 515          |  |  |

|      | 16.3.1 Stationary and ergodic processes                 | 516          |  |  |

|      | 16.3.2 Time average and ensemble average                | 516          |  |  |

|      | 16.3.3 Correlation function                             | 516          |  |  |

|      | 16.3.4 Autocorrelation function                         | 517          |  |  |

|      | 16.3.5 Mean square value                                | 518          |  |  |

|      | 16.3.6 Wiener-Khintchine theorem                        | 518          |  |  |

|      | 16.3.7 Power spectral density                           | 518          |  |  |

| 16.4 | Signals, data and information                           | 518          |  |  |

|      | 16.4.1 Amount of data                                   | 518          |  |  |

|      | 16.4.2 Bandwidth and minimum sample rate                | 519          |  |  |

|      | 16.4.3 Crest factor                                     | 519          |  |  |

|      | 16.4.4 Data rate                                        | 519          |  |  |

|      | 16.4.5 Information rate                                 | 520          |  |  |

|      | 16.4.6 Relevant signal properties                       | 520          |  |  |

|      | 16.4.7 Channel capacity                                 | 520          |  |  |

|      | 16.4.8 Spectral efficiency                              | 521          |  |  |

| 17   | System Modeling (selected topics)                       | 523          |  |  |

| 17.1 | Introduction                                            | 524          |  |  |

| 17.2 | Classification of systems                               | 5 <b>2</b> 4 |  |  |

| 17.3 | Linear stationary instantaneous systems                 | 525          |  |  |

| 17.4 | Linear stationary dynamic systems                       | 525          |  |  |

|      | 17.4.1 Time domain analysis                             | 526          |  |  |

|      | 17.4.2 Frequency domain analysis                        | 526          |  |  |

|      | 17.4.3 Complex frequency domain analysis                | 527          |  |  |

|      | 17.4.4 Time domain analysis using the Laplace transform | 529          |  |  |

| 17.5 | Fixed instantaneous nonlinear systems                   | 530          |  |  |

|      | 17.5.1 Operating point, input and output offset         | 530          |  |  |

|      | 17.5.2 Small-signal gain and inaccuracy                 | 531          |  |  |

|      | 17.5.3 Nonlinearity                                     | 531          |  |  |

|      | 17.5.4 Differential gain                                | 531          |  |  |

|      | 17.5.5 Harmonic distortion                              | 531          |  |  |

|      | 17.5.6 Intermodulation distortion                       | 532          |  |  |

| 17.6 | Linear time-variant instantaneous systems               | 533          |  |  |

|      |                                                         |              |  |  |

| 1/10 | Diricour u | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |     |

|------|------------|-----------------------------------------|-----|

| 17.7 | Modelin    | ng of nonlinear dynamic systems         | 533 |

| 18   | Networ     | k Theory (selected topics)              | 535 |

| 18.1 | Introduc   | ction                                   | 536 |

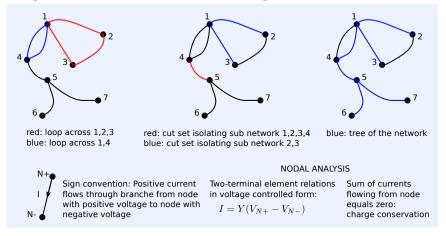

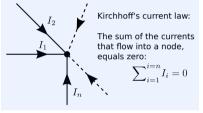

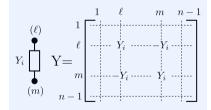

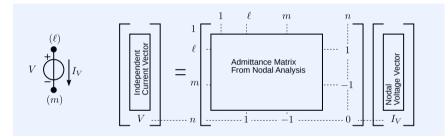

| 18.2 | Nodal A    | nalysis                                 | 536 |

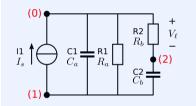

|      | 18.2.1     | The procedure                           | 537 |

|      | 18.2.2     | General form of the admittance matrix   | 540 |

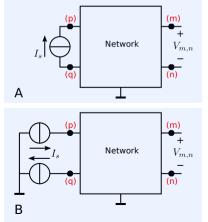

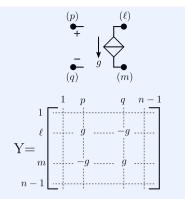

|      | 18.2.3     | Voltage-controlled current sources      | 541 |

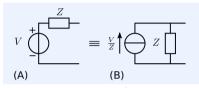

|      | 18.2.4     | Network transformations                 | 542 |

|      |            |                                         |     |

| 543<br>547<br>547<br>552<br>553<br>553<br>555 |

|-----------------------------------------------|

| 547<br>552<br>553<br>553                      |

| 552<br>553<br>553                             |

| 553<br>553                                    |

| 553                                           |

|                                               |

| 555                                           |

|                                               |

| 556                                           |

| 557                                           |

| 557                                           |

| 563                                           |

| 571                                           |

| 572                                           |

| 574                                           |

| 575                                           |

| 577                                           |

| 578                                           |

| 578                                           |

| 578                                           |

| 579                                           |

| 580                                           |

| 580                                           |

| 581                                           |

| 581                                           |

| 581                                           |

| 582                                           |

| 582                                           |

| 583                                           |

| 587                                           |

|                                               |

## **Preface**

## **Structured Electronics Design**

Structured Electronics Design offers strategies, methods, and techniques for electronic circuit design.

#### The complexity of analog electronics

Many people consider analog electronic circuit design complex. This is because designers can achieve the desired performance of a circuit in many ways. Together, theoretical concepts, circuit topologies, electronic devices, their operating conditions, and the system's physical construction constitute an enormous design space in which it is easy to get lost. For this reason, analog electronics often is regarded as an art rather than a solid discipline.

#### Experienced designers and intuitive design

At first glance, there doesn't seem to be a straightforward way to design analog circuits. In daily practice, experienced designers intuitively use all these degrees of freedom to modify and combine known solutions into new ones. However, intuition is knowledge of which the origin has become unclear. It results from a personal internalization process and cannot be shared with novices who have yet to acquire this knowledge. Therefore, intuition cannot and should not be a basis for design education.

The design of electronic circuits can be taught, shared, and understood if presented in a structured way with a distinct formulation of design goals, strategies, methods, and techniques. Moreover, it requires a clear distinction between theoretical concepts and their physical implementations.

#### Structured Electronics Design

Rather than taking numerous existing circuits as a starting point, it is much more effective to start a new design with a clear understanding of

- 1. The application and its environment

- 2. The required functionality

- 3. The implementation technology and physical operating mechanisms

- 4. Theoretical concepts, design strategies, methods, and techniques

All of this needs to be combined to achieve an acceptable performance-cost ratio.

Structured Electronics Design is a systems engineering approach to the design of analog electronics. It places analog electronics design in the perspective of information processing and provides a top-down design method with a bottom-up awareness. The hierarchical design process has a similar structure at each hierarchical level.

Important questions driving the design process are

1. How is the information present in the electrical signals?

<sup>2</sup> also: materializing.

- 2. Which physical signals present in the application environment may degrade the quality of the signal processing?

- 3. In which way and to what extent is the application sensitive to all kinds of information processing errors?

- 4. Which physical operating principles exist for implementing<sup>2</sup> the information processing functions, and to what extent are they available in the desired technology?

- 5. Do the fundamental physical limitations of information processing and technological or economic limitations cause unacceptable design risks?

- 6. Which design methods and techniques are available to maximize the performance to costs ratio of the design?

The first three questions emphasize the top-down approach, the next two illustrate bottom-up awareness, and the last shows the conceptual design approach.

Structured Electronics Design

- 1. Defines a step-by-step design process based on the above questions, and indicates which \*design question\* is answered at each design step.

- 2. Properly orders and orthogonalizes the design steps, based on solid principles from physics, signal processing, control theory, and network theory.

- 3. Helps circuit designers efficiently and effectively obtain the desired performance to costs ratio.

- 4. Provides a solid foundation for circuit design education and automation.

- 5. Has been developed and educated since the 1980s at the Delft University of Technology.

## About the author

Anton Montagne (Leiden, 1953) received his master's degree in electrical engineering in 1984 at the Delft University of Technology. In 1983, he joined Philips Semiconductors in Nijmegen where he designed analog integrated circuits for audio and video applications. At Philips, he also set up training courses on analog electronics. In 1986, he cofounded the product development company Product Partners where he carried out many analog designs in the field of instrumentation. In 1989, together with Catena Microelectronics, Delft University of Technology, and the Institute of Microelectronics in Stuttgart, he cooperated in the development of an intensive training course, covering many topics of analog information processing. Since 1997, he has worked as an independent consultant, trainer, and designer in the field of analog electronics. Over the past 38 years, he developed analog electronics for instrumentation and communication systems for the industry and carried out many training courses on analog electronics at, amongst others, Catena Microelectronics, Philips Semiconductors, Philips Medical Systems, NXP, Ericsson, Plessey, Texas Instruments, ASML, TNO, Bruco IC design, 3T, Carl Zeiss SMT, TMC and ASMPT.

Anton Montagne is the inventor and coinventor of patents in the fields of position sensors, imaging, charge-coupled devices, and high-stability crystal oscillators.

Since 2016 Anton Montagne is coaching students and giving lectures and masterclasses "Structured Electronics Design" at the Delft University of Technology.

## **Acknowledgments**

This book is the spin-off of workshops I have given and the design projects I have participated in over the past 35 years. Writing such a book is never the result of one person's effort. I am indebted to many people I cooperated with and the many students I have taught. They taught and inspired me, and they have contributed in their very own way to its creation.

The design approach for analog electronic signal processing systems, presented in this book, was suggested around 1987 by Dr. Ir. Ernst H. Nordholt. At that time, we both cooperated in educating circuit designers around Europe. Ernst suggested that analog electronic signal processing systems could be designed with a limited number of basic information-processing functions and references. As a result of the fundamental physical limitations of information processing, and due to technological limitations, their performance would deviate from that of their idealized function concepts. The number of signal processing errors, however, could be reduced through the application of a limited number of so-called error-reduction techniques. Limitation of both the number of basic functions and the number of techniques that can be exploited for their improvement helps to solve day-to-day design problems in a structured way and facilitates circuit design education. Moreover, it can be a basis for partial automation of the complex design process.

In the subsequent years, developed design courses based on this approach. In our day-to-day design work, we applied and improved this design method. I am very grateful to have cooperated with Ernst and to be inspired by him. Without this cooperation, this book would not have been written.

Despite my interest in signal processing, during my education in analog electronics, I was primarily focused on all kinds of aspects of circuit design. I am therefore very grateful to have cooperated with Dr. Ir. Huib Dane. His ability to explain complex topics from statistical signal processing helped me with my professional development and inspired me in developing training courses for the design education of professionals.

It has been a pleasure and honor to work together with Catena Microelectronics in Delft. Since 1999 this company offered me the possibility to educate their novice analog IC designers, and in this way, it contributed very much to the development of this material.

I am also very grateful to cooperate with The High-Tech Institute and Ir. Hans Vink. Since 2010. They organize my training courses, which allows me to spend my time teaching, serving my customers, and writing this book.

A special word of gratitude is reserved for my friend Dr. Ir. Jan Deiman. I am indebted to him for the pleasant conditions he offered me in his guest house in Bali, which facilitated the writing of this book in a most inspiring way.

I also want to thank Ir. Dr. Chris Verhoeven from the TU Delft for offering me the opportunity to coach students during the execution of their master thesis and for giving guest lectures and masterclasses at the TU Delft. Cooperation with him very much encouraged me to complete this work. Thanks to him, this book is now used for teaching *Structured Electronics Design* at the Delft University of Technology and, I have the pleasure of working with him. Our conversations about the structured design method, orthogonality, basic functions, and error reduction techniques, were very inspiring.

I also had many fruitful discussions about this material with Ir. Jeroen van Duivenbode, a fellow at the TU Eindhoven. He inspired me in writing the MATLAB version of SLiCAP and contributed the name *servo function* used in this book. I would like to thank Jeroen for this contribution and our pleasant and inspiring cooperation.

While working with this book, many students gave me valuable feedback. I am very grateful for their contributions and encourage everyone to inform me about errata and future improvements.

Edition 3, June 2023 Delft, The Netherlands Anton Montagne

## Introduction

| 1.1 | Electr | conics                                            | 2  |

|-----|--------|---------------------------------------------------|----|

|     | 1.1.1  | Analog Electronics                                | 2  |

|     | 1.1.2  | Structured design                                 | 3  |

|     | 1.1.3  | This chapter                                      | 3  |

| 1.2 | Select | ted topics from systems engineering               | 3  |

|     | 1.2.1  | Basic concepts                                    | 4  |

|     | 1.2.2  | Basic design process                              | 7  |

|     | 1.2.3  | Design data and documents                         | 10 |

| 1.3 | Electr | conic information processing                      | 10 |

|     | 1.3.1  | Basic concepts                                    | 11 |

|     | 1.3.2  | Limitations of information processing             | 12 |

| 1.4 | Struc  | tured Electronics Design                          | 13 |

|     | 1.4.1  | Outline of the design language                    | 13 |

|     | 1.4.2  | Basic functions and basic objects                 | 14 |

|     | 1.4.3  | Performance, costs, and FOM                       | 16 |

|     | 1.4.4  | Error-reduction techniques                        | 16 |

|     | 1.4.5  | Differences with traditional analog design        | 17 |

| 1.5 | This l | book                                              | 18 |

|     | 1.5.1  | What you will know after studying this book       | 18 |

|     | 1.5.2  | Part 1: design of application-specific amplifiers | 21 |

|     | 1.5.3  | Part 2: background knowledge                      | 28 |

|     | 1.5.4  | How to use this book                              | 29 |

<sup>1</sup> L. De Forest. Wireless Telegraphy, Januari 1907

## 1.1 Electronics

The invention of the *Audion* by De Forest, patent [Forest1907]<sup>1</sup>, can be regarded as the birth of electronics. Since then, around the world, thousands of amateurs, scientists, and engineers have contributed to its development. Nowadays, concepts developed in the first decennia of its existence are continuously being adapted for application to new technologies, while new ones are still being developed.

## 1.1.1 Analog Electronics

Although signal processing is mainly implemented digitally nowadays, analog electronics still play a significant role in all kinds of electronic equipment. On the one hand, fast digital processing and strict EMC requirements require knowledge about the continuous nature of electrical signals. On the other hand, interfacing with sensors, actuators, transmission lines, or communication channels often requires information embedded in analog or multilevel digital signals.

Electronics deals with the *manipulation of electrical currents with nonlinear electrical devices*. According to this definition, electronics does not deal with the meaning of electrical signals. However, when designing electronic circuits, one cannot ignore their information processing tasks. This is a consequence of the fundamental physical and technological limitations of information processing:

The amount of information that can be processed by any physical system is limited. This is due to the addition of noise, the limited availability of power and the limitation of the rate of change of signals.

In addition, the physical principles for the implementation of information processing functions are usually imperfect and contribute to information processing errors. For example, the nonlinear behavior of semiconductor devices and vacuum tubes introduces technology-dependent errors into intended linear systems.

Hence, we first need definitions for the *intentional behavior* of information processing systems.<sup>2</sup> Secondly, we need knowledge about the manifestation of information processing errors due to physical and technological limitations. These manifestations depend on how the information is present in the signal. For example, binary digital signals will be less sensitive to nonlinearity than multi-valued digital signals or analog signals.

Usually, information processing happens in an environment where different noise sources adversely affect the signal quality.

Another aspect of information processing is its costs. Electronic information processing requires matter, space, and electrical energy. It also contaminates its environment with temperature rise and EMI.<sup>3</sup>

Apparently, during the design of electronic information processing systems, the designer has to deal with many aspects.

At first glance, there does not seem to be a straightforward way to design such systems. However, the complexity of its design is not unique for analog electronics. Designing cars, airplanes, production equipment, test equipment, and many other modern products is highly complex. Proper structuring of complex design processes is a proven key to their success!

<sup>2</sup> The intentional behavior is also referred to as: the ideal behavior, or the conceptual behavior.

<sup>3</sup> EMI: Electromagnetic interference can be considered as noise.

### 1.1.2 Structured design

There exists considerable literature about structured design methods. It is suggested that interested readers study *systems engineering*, for example [BlanchardEA1998]<sup>4</sup> and [KossiakoffEA2003]<sup>5</sup>. Particularly those who fear a conflict between creativity and structured design methods are encouraged to read [Terninko1998]<sup>6</sup> and [Altshuller1999]<sup>7</sup> about TRIZ, a Russian acronym for *Theory of Inventive Problem Solving*. TRIZ is a generalized design theory that offers discipline and technology-independent design methods and technology.

In this book, we will present a structured approach to the design of negative feedback amplifiers, based on clear concepts from systems engineering, information processing, network theory and control theory. The design approach is also *inspired* by TRIZ.

This book elaborates the work presented in [Nordholt1983]<sup>8</sup> and the work presented in [Verhoeven2003]<sup>9</sup>. It uses SLICAP for deriving and solving design equations.<sup>10</sup> By doing so, it provides a solid basis for (partial) automation of amplifier design.

#### 1.1.3 This chapter

In this chapter, we will introduce and define the basic concepts of *Structured Electronics Design*. In section 1.2, we will summarize basic concepts and techniques from *Systems Engineering*, and in section 1.3, we will review some concepts from electronic information processing. In section 1.4, we will combine these concepts and techniques and outline the principles of *Structured Electronics Design*. In section 1.5, we will summarize what you will know after studying this book, briefly discuss its contents, and suggest how it can be organized in courses.

## 1.2 Selected topics from systems engineering

In essence, *Structured Electronics Design* is a systems engineering approach to analog electronics design. There exist many different definitions of systems engineering, the one below is taken from https://en.wikipedia.org/wiki/Systems\_engineering:

**Systems engineering** is an interdisciplinary field of engineering and engineering management that focuses on how to design, integrate, and manage complex systems over their life cycles. At its core, systems engineering utilizes systems thinking principles to organize this body of knowledge. The individual outcome of such efforts, an **engineered system**, can be defined as a combination of components that work in synergy to collectively perform a useful function.

In this section, we will briefly summarize some topics from systems engineering. In section 1.2.1, we will introduce some basic concepts, such as innovation, development, research, the invention, the product life cycle, the hierarchical organization of the design process, and the idea of considering a design process from a risk management point of view.

In section 1.2.2 we will present a basic design process that can be used at any hierarchical level of the design.

All sub-processes of this design process result in various kinds of data. Design documents are views upon this data, captured over time. In section 1.2.3, we will describe these results in more detail.

<sup>4</sup> Benjamin S. Blanchard and Wolter J. Fabrycky. *Systems engineering and analysis*. Prentice-Hall, Inc, New York, 1981. ISBN: 013-135047-1

<sup>5</sup> Alexander Kossiakoff and William N.

Sweet. Systems engineering principles and practice. John Wiley and Sons, Inc., New Jersey, 2003. ISBN: 0-471-23443-5

<sup>6</sup> Terninko et al. Systematic Innovation, An introduction to TRIZ. CRC Press LLC, USA, 1998

<sup>7</sup> Altshuller. The Innovation Algorithm, TRIZ, systematic innovation and technical creativity, Translated by Lev Shulyak and Steven Rodman. Technical Innovation Center, Inc., USA, 1999. ISBN: 0-9640740-4-4

<sup>8</sup> Ernst H. Nordholt. Design of High-Performance Negative Feedback Amplifiers.

Delft Academic Press / VSSD, 1 edition, 1983-2006. ISBN: 9789040712470

<sup>9</sup> C.J.M. Verhoeven, A. van Staveren, G.L.E. Monna, M.H.L. Kouwenhoven and E. Yildiz. Structured Electronic Design. Kluwer Academic Publishers, Boston - Dordrecht -London, 2003. ISBN: 1-4020-7590-1

<sup>10</sup> SL1CAP; Symbolic Linear Circuit Analysis Program, written by the author (free, open-source, Python-based).

## 1.2.1 Basic concepts

#### Innovation

Innovation can be defined as a process in which the implementation of new ideas results in new markets, new technologies or new products.

#### Product, market and technology development

Mature companies innovate by developing only one of these three at a time:

• Market development:

Development of new markets for existing product-technology combinations

• Technology development:

Development of new technologies for existing product-market combinations

• Product development:

Development of new products for existing market-technology combinations

Simultaneous development of combinations of the above is called diversification. Diversification is considered risky. In practice, it has a very low success rate.

Innovation plans are often presented in road maps. Such maps illustrate the successive development of products, markets, and technologies over time.

#### Research

Research is a process in which one acquires knowledge about something. It must be separated from innovation. Knowledge about products, markets, and technologies, is the basis for their development, and missing knowledge must be identified and acquired before starting a development that needs it.

#### The invention

The innovation process in start-ups usually differs from that in mature companies. The latter ones have a well-defined product-market-technology portfolio and innovate by improving or extending products, markets, or technologies. Start-ups often start with a basic idea based on a discovery or an invention, while they don't yet have a well-defined product-market-technology portfolio. The source of the invention can be a dream, an annoyance, something that somehow pops up in the mind of an engineer, but in many cases also: the result of a structured design process!

#### Product life-cycle processes

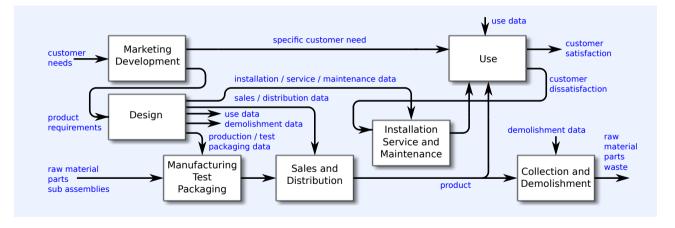

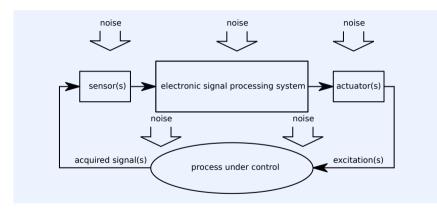

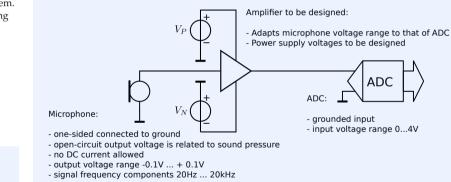

In this book, we confine ourselves to the design of application-specific amplifiers. One important aspect is to determine the requirements of such amplifiers. In general, the product requirements follow from the interests of the stakeholders of the product life cycle processes. Figure 1.1 shows an IDEFo model of the product life cycle processes.

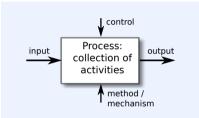

The IDEFo drawing convention for processes is shown in Figure 1.2. A process, is a collection of activities that generates output (right) from its input (left). The process is controlled by its control input (top), and the activities are based on resources, methods, or mechanisms (bottom); see https://www.idef.com/.

The life cycle processes shown in Figure 1.1 are:

- 1. Marketing

- 2. Design

- 3. Manufacturing/test/packaging

- 4. Sales and distribution

- 5. Installation service and maintenance

- 6. Use

- 7. Collection and demolishment

The viewpoint of the model from Figure 1.1 is the data to be generated during the design process. The figure clearly shows that during the design process, data is generated for almost all other life cycle processes. Therefore, the stakeholders of almost all life cycle processes contribute to the product requirements in one way or another.

Fortunately, many of their requirements are covered by regulations and standards. Standardization of components, materials, production methods, and many other aspects enable a short time-to-market and facilitate global mass production.

#### Hierarchically organized design processes

In general, engineers solve complex problems by breaking them down into less complex. In this way, they create a hierarchical structure in which the level of detailing increases at each level of hierarchy. This process ends when all product parts can be purchased or manufactured. Hence, designing is a top-down, hierarchically structured process.

The materialization of the design, however, proceeds bottom-up. Hierarchical levels in this phase correspond with those in the design phase. This way of working makes it possible to perform predefined integration tests of physical (sub)systems at each hierarchical level.

A design process with an identical structure at each hierarchical level facilitates the management of design projects. In section 1.2.2 we will present such a design process.

#### **Risk management**

We have seen that the design of a product is a top-down process, while its materialization is a bottom-up process. As a result, the feasibility of a product

Figure 1.1: IDEFo product life cycle process model. The viewpoint of this model is the data that needs to be generated during design.

Figure 1.2: Business process model according to the IDEFo standard.

is proven only when all components and parts can be purchased or manufactured. Therefore, potential design risks may not manifest themselves until the end of the design process. This, of course, is unacceptable because it causes loops in the design process.

There are several ways to avoid design loops resulting from unforeseen risks:

- 1. Keep the innovation level low:

- (a) Separate research from development

- (b) Avoid diversification

- (c) Identify and justify assumptions

- 2. Start design projects with a risk analysis

- 3. Solve design risks at the hierarchical level of their appearance.<sup>11</sup>

From the above, it is clear that product development can be regarded as risk management. Risks, with the greatest product of their assumed probability of occurrence and their assumed impact, should always be addressed first.

From a risk management point of view, one should not start a design detailing familiar parts of the product. Design risks that will manifest themselves later while designing the unfamiliar parts may force the designer to reconsider the entire structure of the product. As a result, requirements of these previously detailed parts may change drastically, or worse, these parts may no longer be required.<sup>12</sup>

#### Show stoppers

In this book, we will pay attention to the early identification of *show stoppers*.

A show stopper is something that stops or could stop the progress of the design process, such as a performance-cost ratio that cannot be achieved.

Experienced designers are often intuitively aware of the consequences of economic and technological constraints on the design. Therefore they usually intuitively account for them at an early stage of the design process. A novice designer, who is not yet fully aware of the impact of such limitations, may encounter a show stopper for a design proposal at a later stage and may then be forced to reconsider the earlier selection of this proposal.

In general, design risks increase with increasing levels of innovation. Conducting research is the way to reduce those risks.

#### Figure Of Merit (FOM)

Throughout the design process, designers need to select the most promising solution from a set of possible solutions. Such selections are generally based on the *performance-cost* ratio of the different solutions. A *Figure Of Merit* (FOM) is the most compact way to represent the performance-cost ratio. It is the ratio of the weighted product of the performance parameters and the weighted product of the cost factors of a solution:

$$FOM = \frac{product of weighted performance measures}{product of weighted cost factors}$$

(1.1)

$^{\scriptscriptstyle 11}$  Don't let them unresolved so they appear at the next hierarchical level.

<sup>12</sup> Low-hanging fruit may not be consumed first.

### 1.2.2 Basic design process

In this section, we will introduce a basic design process to be used at any hierarchical level. The underlying idea is to consider the product itself, as well as all of its parts, as objects. These objects or combinations thereof perform functions in a physical environment and at the expense of resources, such as matter, energy, time, and space.

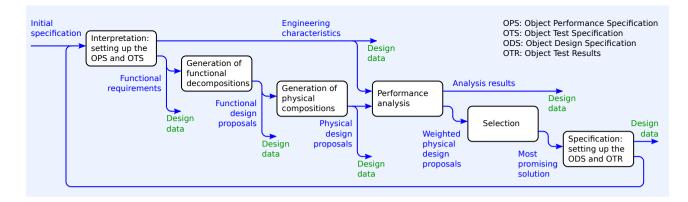

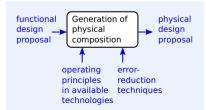

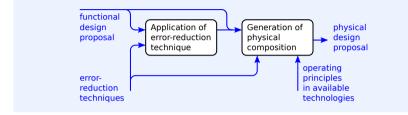

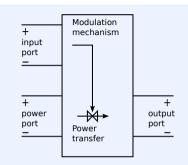

This basic design process is depicted in Figure 1.3. It consists of a series of activities that together define a composition of objects that fulfills the requirements of the main object. The output at the lowest hierarchical level is purchase or production data for the object. At higher levels, the outputs are initial object performance requirement specifications of subsystems. These initial specifications are the inputs at the next hierarchical level. The input at the highest hierarchical level, is the initial specification of the product.

The different activities of this basic design process are elucidated below.

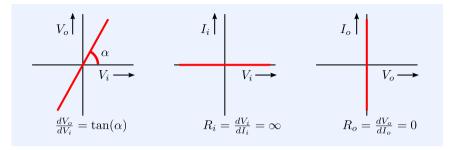

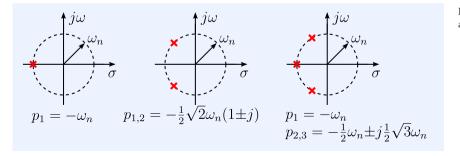

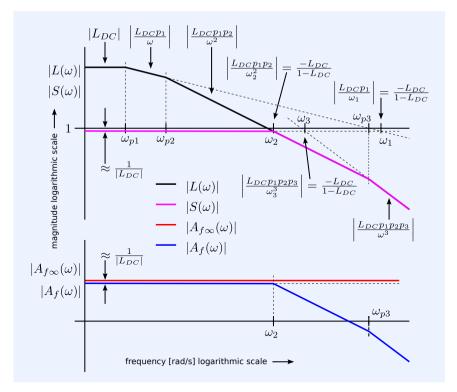

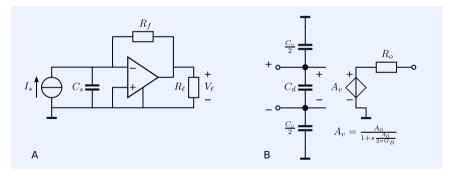

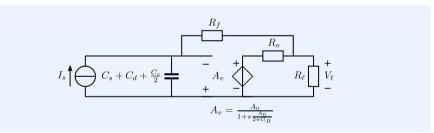

#### **Object Performance Specification (OPS) and Object Test Specification (OTS)**